### AUGUST 2024 DEST CONTROLOGY MAGAZINE

Kris Moyer Instructor, IPC

Boo

"Whether you are new to PCB design or a seasoned designer, this book can help you achieve a successful, high-quality, high-yield PCB design the first time and every time."

### THE PRINTED CIRCUIT DESIGNER'S GUIDE TO..."

### **DFM Essentials**

Anaya Varoya American Standard Circuits ASC Sunstone Circuits

# Your success by the book!

Up your game in 30 minutes. Industry experts share knowledge you can apply immediately to make you (and your company) more successful.

"I-007ebooks are like water in the desert ....it's up to you to drink it in order to survive!"

> Stephen V. Chavez Senior Product Marketing Manager Siemens

#### **VISIT THE LIBRARY**

#### AUGUST 2024 • FEATURE CONTENTS

# **DESIGNOUT** MAGAZINE PCB Design Cost Drivers

What's driving your costs? In this month's issue, our expert contributors explain the impact of cost drivers on PCB designs and the need to think in terms of a design budget. They discuss a myriad of design cycle cost adders—hidden and not so hidden—and ways to add value as well. When every decision has ramifications downstream, the more you know, the better.

#### FEATURE ARTICLES

- **10 Hidden (and Obvious) Design Mishaps With Big Cost Impacts** by Jen Kolar

- **18 Hidden Cost Drivers in PCB Design** by Cherie Litson

#### FEATURE COLUMNS

8 Watch Out for Cost Adders by Andy Shaughnessy

- 22 Commonsense Cost Cutting by Martyn Gaudion

- **34 My Anti-venom to PCB Cost Adders** by Kelly Dack

- **48** An Evolution in PCB Design Costs by Istvan Novak

#### alphacircuit.com

### Ahead, Warp Factor 10!

Inside our new, 44,000 sf technology center, you'll find the most innovative printed circuit board manufacturing equipment the industry has to offer. Our friendly, capable team is dedicated to building your advanced technology boards and delivering a superior customer experience.

Let us help you create the solutions that will power tomorrow's technology.

What can we help you innovate today?

OUR CAPABILITES

**OUR PRODUCTS**

#### AUGUST 2024 • ADDITIONAL CONTENTS

# DESIGNOOT

#### SHORTS

- 9 The Nexus of Chinese and American Business Relations

- **39** BOOK EXCERPT: The Printed Circuit Designer's Guide to... DFM Essentials

- 45 A Comprehensive Guide to Navigating Cost Drivers and Sustainability in PCB Production

- 70 Plasma Irradiation Transforms Tllurium's Electronic Properties

- 75 Creating Artificial 'Muscles' for Safer, Softer Robots

#### DEPARTMENTS

- **79** Career Opportunities

- 86 Educational Resources

- 87 Advertiser Index & Masthead

#### COLUMNS

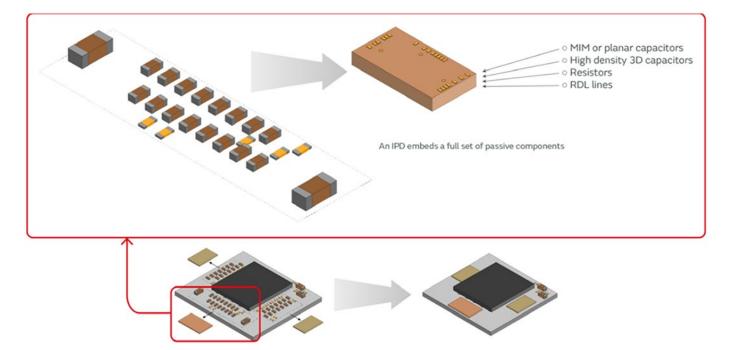

- 64 Integrated Passive Devices: Design Solutions With Many Benefits by Joe Fjelstad

- 72 Designing for Reality: Electroless Copper by Matt Stevenson

#### **ARTICLES & INTERVIEWS**

- 28 Cost-optimize Your PCB Design and Specifications by Erik Pedersen and Richard Koensgen

- 40 Impact of the Altium-Ansys Partnership on PCB Design by Josh Moore

- 54 Asymmetric Hybrid Printed Circuit Board Design– Warpage Considerations by Kaspar Tsang et. al.

- 58 Dan Beeker: Outstanding in his 'Fields' An I-Connect007 Interview

- 68 UHDI Applications for Aerospace by Anaya Vardya

#### HIGHLIGHTS

- 46 MilAero007

- **76** Top Ten Editor's Picks

6 DESIGN007 MAGAZINE I AUGUST 2024

### Enable 800GbE Ethernet Speed with EM-892K and EM-892K2 Materials

Industry's First Halogen-free Extreme Low Loss (ELL) Laminates

Key Material Features: EM-892K @70%RC: Dk: 2.84/ Df: 0.0017 @10GHz EM-892K2 @70%RC: Dk: 2.76/ Df: 0.0013 @10GHz with Cavity Resonator Method

Lead-Free Soldering Test: PASS LF-260°C/ 10X with 32L 0.6mm hole pitch

Anti-CAF Test: Pass 100V/ 85°C/ 85% RH with 32L 0.6mm hole pitch for 1K Hours

IST Test: Pass Room temperature to 150°C for 3K Cycles with 32L 0.6mm hole pitch

Advanced Foil Availability: Both HVLP3 and HVLP4 are compatible with "Glicap" non-etch oxide treatment

Hybrid Compatibility: Fully compatible with EM-370(Z) (Mid. Loss) material for cost reduction and pass LF-260 10X with 32L 0.6mm hole pitch

North American Master Distributor (949) 587-3200 • insulectro.com

# Watch Out for Cost Adders

#### **The Shaughnessy Report**

by Andy Shaughnessy, I-CONNECT007

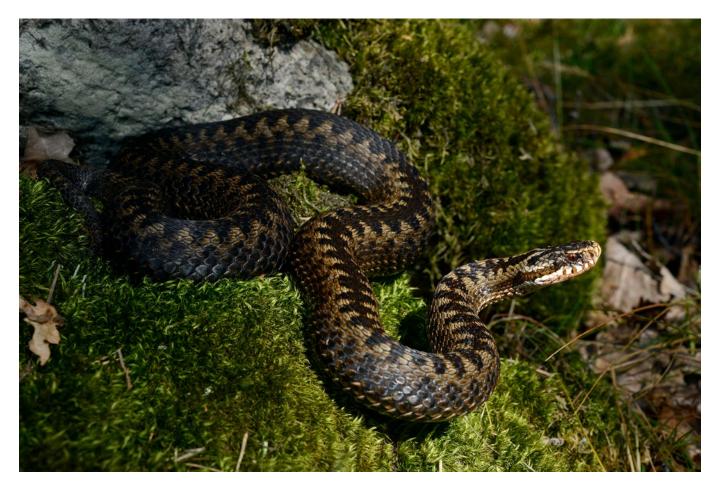

I've owned a few snakes in my lifetime. In my high school biology class, for example, I took care of our black rat snake for a few weeks. He escaped once, which they all eventually do, and climbed up inside our furnace. My next snake was a nine-foot yellow-tailed python. He suffered an ignominious end when he was killed by the giant rat who was supposed to be his dinner. In my 20s, I had a hognose snake that also escaped, and I never did find him. Snakes can be tricky, as you can see. This month we focus on one serpent that bedevils PCB designers and design engineers: the cost adder.

Because approximately 70% of the manufacturing costs of a product are determined in the design cycle, every decision a designer makes has some effect—good or bad—on the manufacturing cost, as well as the cost of the final product.

Fortunately, cost adders can be kept at bay: Designers can employ hundreds of tips, tricks, and techniques to keep costs down.

In this month's issue, our expert contributors explain the impact of cost drivers on PCB designs and the need to consider a design budget. They discuss the myriad design cycle cost adders—hidden and not so hidden—and ways to add value. When every decision has ramifications downstream, the more you know, the better.

We start with Jen Kolar's article on common design errors, especially DFM miscues, that can have a bigger impact on cost than you might think. Cherie Litson details areas where she often discovers cost adders hiding, and which teams seem to be constant targets of these troublemakers. Columnist Martyn Gaudion offers "commonsense" tips for adding value to the design cycle. Kelly Dack provides "anti-venom" for PCB design cost adders, and he points out some of the dens where cost adders often lurk, waiting to drive up your manufacturing costs. Michael Marshall has a paper on design cost drivers, which covers dozens of ways designers can add cost into the design cycle, often without realizing it. Rounding out our features is a column by Istvan Novak on the evolution of PCB design costs.

We also have columns by Matt Stevenson and Joe Fjelstad, and articles by Dan Beeker, Erik Pedersen and Richard Koensgen, and Anaya Vardya, as well as an excerpt from Anaya's brand-new book, *The Printed Circuit Designer's Guide to DFM Essentials.*

I hope you're having a relaxing summer. You've earned a vacation. **DESIGN007**

Andy Shaughnessy is managing editor of *Design007 Magazine*. He has been covering PCB design for 23 years. To read past columns, click here.

#### **GLOBAL CITIZENSHIP**

#### The Nexus of Chinese and American Business Relations

by Tom Yang, CEE PCB

Many people I talk to feel there are very few similarities between how Americans and Chinese do business. However, I believe that's not true. That's why I researched the similarities between our cultures for this second column on global citizenship.

#### Americans Built the Chinese PCB Industry

Remember, it was American companies that taught China how to manufacture circuit boards. Our factories have your fingerprints all over them. So, it should come as no surprise that Chinese and American business practices—while shaped by distinct cultural, historical, and socio-economic factors—nevertheless share several similarities. We still mostly use Western-made equipment and follow IPC standards developed in North America and Europe.

As we have grown more independent in recent years, for example, in manufacturing our equipment and laminates, our commonalities are becoming more relevant as globalization and technological advancements intertwine the economies of both nations. Understanding these similarities can foster better communication, collaboration, and mutual respect between Chinese and American business professionals.

To continue reading this column click here.

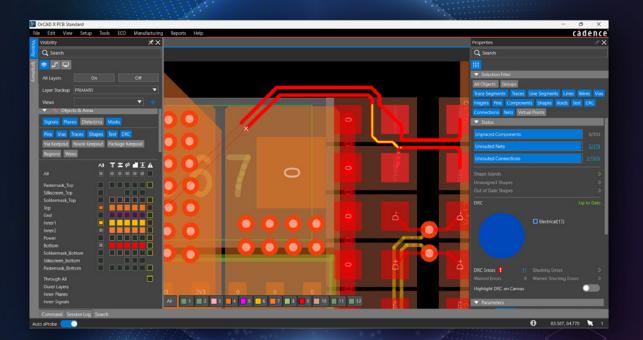

### Hidden (and Obvious) Design Mishaps With Big Cost Impacts

Feature Article by Jen Kolar MONSOON SOLUTIONS

At Monsoon Solutions, we provide PCB layout services for the full lifecycle of products, from one-off prototypes to items manufactured in production volume. We also manage manufacturing and assembly for prototype and smaller production runs for both customerproduced and in-house layouts. As a result, we see various manufacturing data packages and work with many different manufacturers. I asked our PCB design engineers and program managers to share the cost adders and cost savers that designers can affect, and it was interesting to see that in addition to more technical responses, some of the biggest culprits were rather simple.

#### **Fabrication Note Errors**

Starting with PCB fabrication, one of the most obvious and simplest cost adders is incorrect or missing fabrication notes. As designers, we all like to have a starting point for a layout rather than having to start from scratch, and that often means starting from a similar board, which comes with existing fabrication notes. As a service bureau, we also often work on revisions of designs, and thus we inherit fabrication notes from the previous design. A common mistake I see from designers is when they leave notes the new designer doesn't understand or know if they are required. I will often see them ask the customer about the notes,

### Support For Flex, Rigid Flex and Embedded Component Designs Now Available.

- Import and Visualize Flex, Rigid-Flex and Embedded Component Designs

- 3D Visualization to Validate PCB Construction and Component Assembly

- Manage Variable Stackup Zones for Rigid-Flex Designs

- Easily Create Custom Flex or Rigid-Flex Fabrication and Assembly Documentation

#### For more information visit downstreamtech.com or call (508) 970-0670

and it's not uncommon for the customer to not know if they apply either. Rather than removing them, they commonly remain "just to be safe." This often leads to extra processes like via fill, planarize, and plate. It may lead to building to Class 3 vs. Class 2 or extra testing and paperwork requirements. It may lead to adding hard gold vs. just ENIG. It may lead to ordering more exotic materials where standard FR-4 was fine. It also can lead to back-and-forth DFM questions as the fabricator must confirm what does or doesn't apply, and with which offshore vendors can mean delays of multiple days.

Similarly, if there are no fabrication notes, the fabrication vendor is left guessing and may choose processes or materials that are more expensive or not absolutely needed, or they may miss important aspects of the design, like controlled impedances or that a specific thickness is needed for edge connectors. Make sure to review your notes for clarity and correctness before sending them to the fabrication shop. If you are unsure how to specify your requirements, talk to your fabricator.

Another fabrication note mishap is not calling out whether the boards should be v-scored or have mouse bites for breakaway tabs. It is common for offshore high-volume designs to

### "If you are unsure how to specify your requirements, talk to your fabricator."

use tabs without scoring or mouse bites and for assemblers to have the tools necessary to depanelize them. This is rarely the case in lower-volume or prototype shops. I have seen countless cases of a customer providing data from a previous high-volume production build that included solid tabs that smaller prototype assembly shops were not able to easily depanelize. If the assembly house is unable to depanelize the board correctly, this could lead to damaged boards, damaged components, and a possible respin of the boards. Verify with your assembly house on how they will want to depanelize the boards and add that to your fabrication notes for your fabrication shop.

Copper thieving callouts are a less common fabrication note mistake, but still one that can cost an entire build to be scrapped. It is common for RF boards to have intentional voids that you don't want any copper added to, like thieving. Make sure your fabrication notes clearly specify if thieving can be added, and where on the board it should be avoided. I've seen frustrated customers find out after days of debugging assembled boards that they aren't working as expected due to thieving being added to areas where it shouldn't be. There is no salvaging this mistake; it's a respin.

Now let's address vias-in-pad in thermal ground pads under ICs. In most cases, assemblers will windowpane the stencil to distribute the paste and it's not at all an issue to have non-filled vias in larger center ground pads. If your design doesn't otherwise need via-inpads filled, then don't call it out for your IC thermal ground pads. Make sure your fabricator knows they don't need to be filled or they might assume they do.

Finally, make sure your fabrication notes clearly call out where parts overhang so that they don't panelize it in a way that they can't be assembled in panel. Forcing assemblers to work "one-up" vs. in array adds cost and time. This is an area often missing from fabrication notes and one that would save a lot of frustration for the assembler if it were added.

#### **Design Mishaps**

As designers, it's our job to make sure the PCB functions correctly and meets the required specifications. We spend most of our time in design making sure the board meets our internal or customer specifications, but the fabrication and assembly specifications are just as important when trying to avoid increases in cost.

Poor footprint design can often lead to added costs in manual rework, additional stencil orders, and poor yield. One of the most common footprint errors is missing solder mask openings. Missing openings are typically discovered after a stencil has already been ordered, and results in the assembler needing to scrape solder mask off pads and reorder stencils to salvage the build. This kind of rework is not always possible, and if the assembler can't make it work, another set of corrected PCBs will need to be ordered.

A favorite error of mine, and of many assembly shops, is when two designs are panelized together, and they share designators. There are many beneficial use cases to panelize boards together, such as multiple boards that will always be used in a set and share a stackup, but make sure to either do the designs in the same schematic and database or verify that you don't share designators between the designs. A simple way to do this is to use a matching prefix number on your designators for each design. Design A uses C1XX, R1XX, and U1XX, while Design B uses C2XX, R2XX, and U2XX. Also be aware that if too many different boards are together in one array, you can end up with a mismatch of component density across the panel, which can cause warpage during assembly. Combining designs on one panel is often a cost savings attempt that can create more headaches and time cost down the road.

A general area that I can't stress enough in design is the KISS factor: Keep It Simple, Stupid. If you don't need trace width and spacing under 6/6 mils, don't use it. If you don't need microvias, don't use them. If you don't need blind or buried vias, don't use them. If you don't need via-in-pad, don't use it. If you don't need a really tight via/pad aspect ratio, don't use it. If you don't need your components as absolutely as close together as possible, don't do it. Even if you design to Class 3, but your prototype build only needs to be to Class 2, make sure to let the fabricator know. Your fabricator may specify that they can build boards at a 3-mil trace and space, but this doesn't mean they can do it at 100% yield, and the added cost of those failed boards gets passed on to you and your customer.

Newer designers tend to use more complicated via structures, smaller features, and tighter spacing to make routing a design easier. Not only does this drive up cost in manufacturing, but it also adds time, and risks yield and

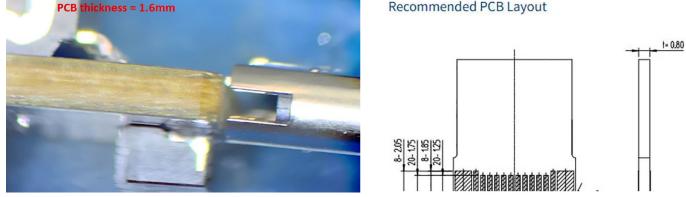

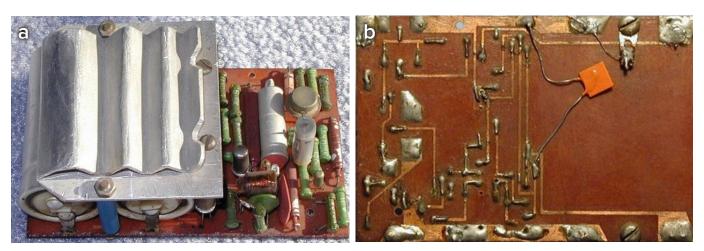

In this mishap case we have a size profile of a board that was intended to insert into another connector. The customer didn't specify a stackup or an overall thickness, so a standard one was chosen by the fab vendor that was too thick. We had to scrap and rebuild.

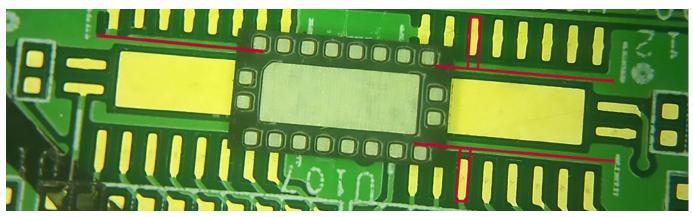

The footprint was incorrect for this part. You can see the part upside down in the middle and in two locations it was to be placed right underneath the part body. Since this was a pick and place part, the issue wasn't found until X-ray inspection after assembly reflow, so the parts had to be manually removed from each board and the boards cleaned up. As this was a multi-lam build and expensive, we wanted to salvage the boards. This mistake ate up time for everyone. It was a prototype run that was fixed on a later rerun. (Right) What we chose to live with after replacement part.

reliability. It takes more time, skill, and experience to keep a tighter design using throughhole vias, and it's not always possible depending on the pitch of parts, or other electrical requirements, but when it is, that can be worth it in saved manufacturing cost.

This brings up another cost adder that designers and customers may not think about, which is the tradeoff of one-time/upfront costs in design vs. repeated costs in manufacturing. There is often a push to get a design to fabrication as quickly as possible. However, if the designer just had a bit more time, maybe the design could've been done without microvias or via-in-pad, or maybe they could've done it in fewer layers. Designers should try to push back on unrealistic customer schedules and expectations and help explain the benefits of taking the time to do it "right." Remembering that PCB design is fairly late in the product design lifecycle, designers are usually pressured to make up time and are given unrealistic schedules. This leads to mistakes or shortcuts that can result in scrapped boards, which means respins, and that means a lot of lost money and time.

Take time to learn about how the fabrication process works. It is a common mistake for newer designers to create via structures that are impossible to fabricate or stackups that are overly complex and add unnecessary lamination cycles. Sometimes customers drive these complex stackups; designers should push back and help the customer understand the fabrication process and how additional lamination cycles drive up cost. Customers can also be the ones driving use of tight aspect ratio holes or tight placement of parts. Help them understand the risks.

Similarly, take time to learn about how the assembly process works. I've already talked about several assembly issues related to panelization, but something as simple as component placement can drive up costs. Don't place very tall parts next to very short parts. Don't place through-hole parts very close to SMT parts. Space out your parts as much as you can, so rework is a possibility. Make sure to turn those courtyards on while you work on placement. Also, remember to add fiducials, both on the board and on tight pitch, larger BGA, QFN, and other leadless packages.

IPC standards exist for a reason. Know them. They aren't just suggestions. Whenever possible, follow them for both PCBs and PCBAs. If you are knowingly violating a standard, try to

#### **BENDING THE POSSIBILITIES**

#### BY TAIYO

AVAILABLE IN AMBER

AMBER

- 🐨 Excellent bendability

- 🐨 High Resolution by photolithography

- 😵 High Reliability

- Simplified process

- **VL94 VTM-0 certified**

- S Low spring back force

- 𝐨 Resolution Line/Space=50/50µm

- Solder mask defined opening (30µm diameter)

#### **OUR BIGGEST FLEX YET!**

Contact your local sales representative today!

Visit www.taiyo-america.com for more information.

Two different versions of the same problem: The pins on this part didn't match the hole. Attempt 1 (left) we were able to Dremel the pins and fit in the holes. Attempt 2 (right) we ended up gluing the part on the board and soldering wires on the pins and board to jumper it together.

limit it to as little of the board as possible and make sure your vendors are aware in advance of starting the build. If you don't follow the standards, you risk an expensive or unbuildable board.

Speaking of vendors being aware, one key to saving cost and time is to ensure that complex designs have preliminary reviews early on by the fabricator and assembler. Nothing is worse than spending months on a design only to find out it is not buildable, it is incredibly expensive to build, or can only be built as a one-off with low yield. Review and validate your design rules early and perform a DFM check with representative data as early in the design as possible. It is common to have fabrication vendors approve a preliminary stackup, via structures, and spacing only to realize that once they see the density of the design or the impedance requirements that it is not possible. This requires redoing the design which adds time and cost.

If you know a design will ultimately be a smaller form factor, design your earlier versions to that so you aren't wasting hours redoing the design. Even if you can get away with some shortcuts in prototype runs, avoid them, or you will have to redo the work when you get to the production version. Do it right the first time. This can be a very hidden cost that the designer isn't initially aware of. Ask your customer what their final plans are for the design so you can

In this case, customer did the layout and didn't include pads for the 4 outer pins of the connector. We had the option of having the shop scrape off the solder mask and manually work the connector in, DNP, or scrap. For this build they chose DNP to salvage it and not spend more cost on the rework.

design to that from the beginning. If they will eventually build to Class 3, set your vias and spacing up accordingly from the beginning. Otherwise, you could be looking at a costly redo to try to add larger pads in a dense design.

This brings us to one of the most important topics and a good closing point: Communicate early and often. Make sure you know all the requirements up front, including mechanical, electrical, budgetary, schedule, and so on. Designers must make a lot of decisions as they are working. If you make them without realizing there are unknown requirements, like keep-outs, high-voltage areas, mounting holes, or testing requirements, you may have a lot of work to redo. We all know time is money. In this case it also can be a sacrifice to quality in an attempt to salvage work done that would have been done differently if the requirement had been known in the first place. Take the time to tell your customers what can be done to make the design better and save them money. They hired you to be the expert, so be one. DESIGN007

**Jen Kolar** is the vp of engineering at Monsoon Solutions, a PCB design service bureau in Bellevue, Washington. Sign up now and exhibit for under \$1500!

Anaheim Electronics & Manufacturing Show

Exposition & Seminar Program Oct. 2nd, 2024 - 10 AM - 5 PM Oct. 3rd, 2024 - 10 AM - 3 PM

Great opportunity for high return on investment. Hosted at the beautiful Anaheim Convention center. Free attendance and parking provided for attendees.

#### Thousands of Industry Professionals Attend

#### Telecom Manufacturers

- Defense Contractors

- © Plastic Molders

- Device Companies

- Machine Shops

- Sports Product Developers

- Contract Manufacturing

#### www.anaheimshow.com

### **Hidden Cost Drivers in PCB Design**

Feature Article by Cherie Litson, MIT, CID/CID+ EPTAC

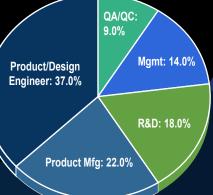

I recently taught a CID+ course, and if you've ever taken a CID or CID+ course, you know that we discuss cost adders quite a bit. When I asked the class of 15 design engineers their ideas on the biggest cost adders, the first and strongest response: the project manager.

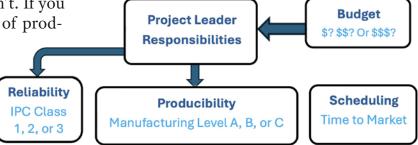

Are you surprised by their answer? After over 40 years in the industry, I wasn't. If you step back and look at the process of prod-

uct development, you'll see that many decisions that affect costs down the line really do take root with the project manager.

After reviewing my own experience and that of many other designers, I referenced my favorite source for defining cost adders: the IPC PCBA Checklist 17. Here you'll find most of the cost adders that we all encounter to one degree or another. As you review the checklist and see who is responsible for many of the decisions, you'll find it all starts with the project leader.

Figure 1: Many of the added—or saved—costs in the PCB design process start with the project leader.

# CEE cares about technology

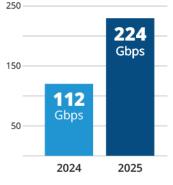

Ethernet SerDes rates will double in the next year

We are committed to staying on the forefront of technology.

CEE has implemented and continues to adopt the latest processes and materials to provide our customers with the best solutions for their high speed applications. One of these is Ultra Low-Loss FPC Application (ULL FPC).

ULL FPC technology can improve signal integrity, bandwidth and reach for high-performance system architectures. For short or mid distance, using ULL FPC to replace PCB transmission lines or high-speed cables, it will achieve loss budget and/or reduce material costs.

#### **CEE: The Global PCB Company**

Everything you've read about the cost-saving process is controlled by the project leader's actions; the project leader is like the chef in the kitchen.

The engineers and designers will then limit their decisions based on the requirements set by the project leader. They become the "sous chef" in the process. The engineers and designers then set the limits and specifications in their documentation affecting purchasing, fabrication, assembly, and test. They become the "station chef" or "line chef." That's why the CID and CID+ classes focus so much on the design engineer's decisions. But no one really

addresses or guides the project leaders for their role in the cost saving process.

So, project leaders, this is for you. Here are some guidelines for getting those cost savings you so desire.

#### 1. Start With the Team

The first cost saving method starts with the team. Having all the input possible at the very beginning and periodically during the project development allows all players to realize the impact of their decisions.

Team meetings can be online and/or in person. Representatives from all those working on the product development should attend. A good project leader has regular design reviews to be sure everyone has input to the project. No finger pointing. True input and problemsolving generate creativity and real cost savings. This is not an easy task. Setting limits for the product features and defining what goes into this model and future models is critical for making sure everyone works toward the same objectives.

#### 2. Identify What Can Be Done

The second cost-saving method is to identify what can and cannot be done concurrently. Many times, this depends on the product's maturity. Look at what can be reused from previous products and designs. If one group is waiting for information from another, discover what else they can contribute to the overall completion of the project.

When designers are waiting for input, they

| E Responsible |                                         | Demand on Assembly                                                                                                            | <b>IPC Standard</b>                                              | Information                                                                                                                                               | Check |  |

|---------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|

|               | Project Leader                          | IPC Class 1, 2 or 3?                                                                                                          | IPC-2221                                                         | Any Additional/Exceptions                                                                                                                                 |       |  |

|               | Project Leader                          | IPC Level A, B or C?                                                                                                          | IPC-2221                                                         | Any Additional/Exceptions                                                                                                                                 |       |  |

|               | Project Leader                          | IPC Level A, B, C or D?                                                                                                       | IPC-1752                                                         | Material Declaration                                                                                                                                      |       |  |

|               | Project Leader                          | RoHS 1 or RoHS 2?                                                                                                             |                                                                  |                                                                                                                                                           |       |  |

|               | Project Leader                          | Touch up and Repair allowed?                                                                                                  | IPC-7711/21                                                      | Valid for both printed board and printed board<br>assembly?                                                                                               |       |  |

|               | Project Leader                          | Surface finish on components?                                                                                                 | J-STD-002                                                        | Different surfaces have different wetting. Can<br>be of importance for achieving IPC Class 3.                                                             |       |  |

|               | Project Leader                          | Process Sensitivity Level (PSL)                                                                                               | IPC-020 and<br>IPC-075                                           | Max Temp, Thermal gradient and H <sub>2</sub> O<br>Sensitivity.                                                                                           |       |  |

|               | Project Leader                          | Surface finish on Printed Boards?                                                                                             | IPC-4552,<br>IPC-4553 and<br>IPC-4554                            | Different Surface Finishes have Different wetting and durability.                                                                                         |       |  |

|               | Project Leader                          | MSL on components                                                                                                             | J-STD-033                                                        | Moisture Sensitive Level of more importance<br>for a Pb-Free process.                                                                                     |       |  |

| 0             | Project Leader                          | Marking and Labeling of Components,<br>printed boards and Printed board's<br>to Identify Pb, Pb-Free and Other<br>Attributes. | J-STD-609                                                        |                                                                                                                                                           |       |  |

| 1             | Project Leader                          | Voids?                                                                                                                        | IPC-7095                                                         | In the balls of BGA and CSP components                                                                                                                    |       |  |

| 2             | Project Leader                          | UL class?                                                                                                                     |                                                                  | Underwriters Laboratories                                                                                                                                 |       |  |

| 1             | Project Leader                          | Cleaning and Conformal Coating                                                                                                | IPC-CH-65                                                        | See Checklist I, page 19.                                                                                                                                 |       |  |

| 4             | Electronic Designer                     | EMC on the printed board and<br>components?                                                                                   | Needed for CE<br>marking                                         | Different Standards/Demands in different<br>countries?                                                                                                    |       |  |

| 5             | Electronic Designer                     | Impedance?                                                                                                                    | IPC-2141                                                         |                                                                                                                                                           |       |  |

| 5             | Electronic Designer                     | High speed/frequency?                                                                                                         | IPC-2251                                                         |                                                                                                                                                           |       |  |

|               | Electronic Designer                     | High amperes?                                                                                                                 | IPC-2152                                                         | Electron State and                                                                                                                                        |       |  |

| B             | Electronic Designer                     | Base material properties for<br>mechanical, electrical and thermal?                                                           | IPC-4101                                                         | All Base Material have different values for Tg,<br>Td, Dk and CTE.                                                                                        |       |  |

| 3             | Project Leader                          | Cooling in- & outside printed boards?                                                                                         | IPC-2221                                                         |                                                                                                                                                           |       |  |

| )             | Electronic Designer                     | Cu foil quality?                                                                                                              | IPC-4562                                                         | Different Cu Foils in the market                                                                                                                          |       |  |

|               | Electronic Designer                     | CAF base material?                                                                                                            | IPC-9691                                                         | Conductive Anodic Filament                                                                                                                                |       |  |

|               | Electronic Designer                     | Embedded in the Assembly?                                                                                                     | IPC-7092                                                         |                                                                                                                                                           |       |  |

|               | Electronic Designer                     | BGA/CSP on the Assembly                                                                                                       | IPC-7095                                                         |                                                                                                                                                           |       |  |

|               | Electronic Designer                     | QFN on the Assembly?                                                                                                          | IPC-7093                                                         |                                                                                                                                                           |       |  |

| 5             | Electronic Designer                     | Flip Chip on the Assembly?                                                                                                    | IPC-7094                                                         |                                                                                                                                                           |       |  |

| 5             | Electronic Designer                     | Minimum isolation distances between<br>holes and tracks?                                                                      | IPC-2221 and<br>IPC-2222                                         |                                                                                                                                                           |       |  |

|               | Electronic Designer                     | Final size (LxWxT)?                                                                                                           |                                                                  | The second statement of the second parts of the                                                                                                           |       |  |

|               | Electronic Designer                     | Number of layers?                                                                                                             | IPC-4121                                                         | Buildup of an multilayer printed board                                                                                                                    |       |  |

| )             | Electronic Designer                     | Mechanical tolerances?                                                                                                        | IPC-2615                                                         | Mechanical Drawings Standard                                                                                                                              |       |  |

| 1             | Electronic Designer                     | Assembly SMDx1, SMDx2 THT or in<br>combination?                                                                               |                                                                  |                                                                                                                                                           |       |  |

| 1             | Electronic Designer                     | Predestinated component placements<br>and forbidden areas?                                                                    | IPC-7351                                                         |                                                                                                                                                           |       |  |

| 2             | Project Leader &<br>Electronic Designer | Documentation requests material declaration                                                                                   | IPC-2611,<br>IPC-2612<br>IPC-2612-1,<br>IPC-2614 and<br>IPC-2615 | If not all needed data are included, the<br>interface between CAD and CAM at the<br>printed board and printed board assembly<br>supplier will be unclear. |       |  |

#### **Checklist at the Project Start Level**

Figure 2: A marked-up excerpt from the IPC PCBA Checklist 17.

can do the following: Research, get training, start mock designs and templates, perform library maintenance, and assist others with their tasks. This can often contribute to speeding up the design process.

While waiting for input, engineers (electrical and mechanical) can do the following: Component engineering and end-of-life verifications on components, be trained on software, research new manufacturing methods, identify critical test criteria, double-check their schematics for wording and pin connections, and work closely with purchasing to certify alternate sources.

Be cautious of purchasing "deals." Make sure it will work with the design. Many good designs have gone bad because a part wasn't available and the new one didn't meet the "form, fit, and function" criteria. Or the panel excising method was changed from "routing" to "scoring" and there wasn't enough clearance to the board features for that process and breakage happened due to mechanical stresses.

For manufacturing, timing is critical. Fabricators shouldn't get too far ahead of the finished design or be caught unaware of what their needs will be. Keep the board shop in the loop for what you plan to do. Your fabricator may need to review your layer stackup to purchase new or additional material. Assembly may need to take early action for component procurement. Many times, manufacturing can offer solutions they have used with other clients.

#### 3. Design Once, Build Many

The third cost saving method is to remember this mantra: "Design once, build many." Take the time to design thoroughly. Doing this can often support going directly from prototype to build. I've done this with new designs. A great chef never serves an undercooked meal.

Designing a board only once also cuts production costs. There is no real need to keep building multiple prototypes with fixes in the product. Quit paying for wasted supplies and time for multiple turns. Quit paying for "fixes" in the production runs. We have incredible software products to support mechanical and electrical analysis of any product, so use them.

#### 4. Educate Yourself

The fourth cost saving method is to educate yourself. Since the PCB design process often becomes the hub of the project, take the CID exam. (Yes, I teach it, but the CID really is a great idea.) Get to know the terminologies and processes involved in designing and manufacturing the board. You don't have to be an expert; just be familiar with all the parts of the processes and be able to plan with them. You may discover new ways to speed up the process and cut costs.

The entire team needs to be able and willing to check themselves and each other. Be willing to explore and learn new methodologies and processes. Every design is different. Every manufacturer has different capabilities. Everyone needs to be open to new suggestions. Be sure to do it in a supportive manner.

One of my dad's favorite lines when he saw someone struggling with a task was, "Would you like to learn another way to do that?" While his suggestions didn't always work, we both learned new options and gained a better understanding of how to accomplish the same thing. Maybe the way we've always done it just doesn't work as well as it did, and there are other ways to accomplish a specific task, process, or goal from a different perspective.

Finding the keys for getting the most "bang for your buck" starts by finding the cost adders for each design. **DESIGN007**

Cherie Litson, MIT CID/CID+, is the founder of Litson1 Consulting and an instructor at EPTAC and Everett Community College. She has more than 30 years of design experience, and has

been an instructor since 2003.

# Commonsense Cost Cutting

#### **The Pulse**

Feature Column by Martyn Gaudion, POLAR INSTRUMENTS

One difference between engineering and pure science is that engineers (in most situations) are looking for cost-effectiveness. They do so by designing the most appropriate level of technology to maximize profitability with acceptable levels of application functionality.

One area that is often overlooked is the energy cost of PCB production. At a recent EIPC conference, Dr. Maarten Cauwe of IMEC in Belgium presented a combined study of the lifecycle impact (LCI) of electronics systems and subassemblies<sup>1</sup>. The study looked at the supply chain as well as the energy impact of HDIs, the power consumption of repeated plating cycles, and the energy impacts of different metal finishings.

One side point was the move to lead-free soldering, which has raised energy consumption across the board. I wonder if legislators will hear this message and, at some point, cause a U-turn in the industry where the lead-free project, once deemed worthy, no longer seems like a good idea. Half a century ago, CFCs were miracle chemicals. Now, not so much. Changing times and emphasis, with effects that take decades to emerge, mean that ideas that once seemed sensible can, with the benefit of hindsight, seem not so good. The study is interesting

Hmm, what is recommended minimum distance for copper to board edge?

PCBs are complex products which demand a significant amount of time, knowledge and effort to become reliable. As it should be, because they are used in products that we all rely on in our daily life. And we expect them to work. But how do they become reliable? And what determines reliability? Is it the copper thickness, or the IPC Class that decides?

Every day we get questions like those. And we love it. We have more than 600 PCB experts on 3 continents speaking 19 languages at your service. **Regardless where you are or whenever you have a question**, contact us!

#### What's your PCB question?

www.ncabgroup.com/faq-about-printed-circuit-boards/#ask

#### Reliable answers. Reliable PCBs.

because it attempts to put together a whole-oflife model for the electronics ecosystem rather than looking at individual items in isolation.

#### **Detail Matters**

While IMEC studies are effective from a top-down standpoint of the whole energy cost of electronics and subsystems, at the day-to-day level, it is down to individuals and teams to make a difference. Additionally, the cost of PCB design is not solely down to energy, though that plays a part at every point. The fact that the type of build alone can impact the cost should be considered, as well as the material choices.

When considering materials for high-speed boards, especially those intended for volume use, it is wise to assess whether each layer needs high-speed materials. The savings can be considerable if basic materials can be used in layers where speeds are low or moderate. Clearly, a different approach is required for low volume. However, if the volume is low because of a prototype application, it's worth exploring the same material choice used in volume to preempt any surprises should you prototype in an exotic material and back off the specs on less critical layers in final production quantities.

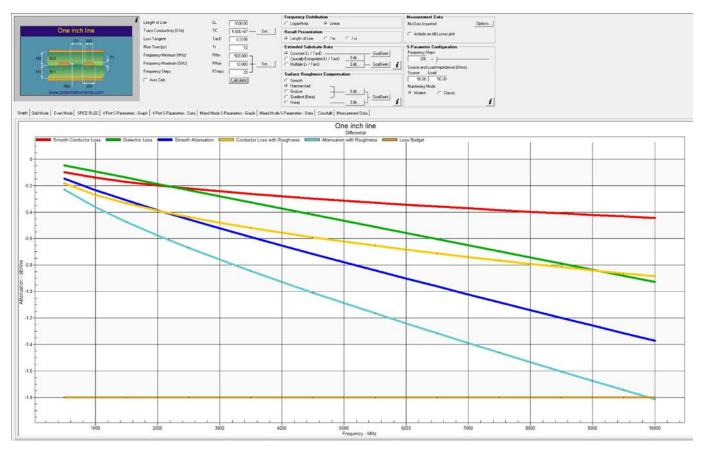

#### Short, Slim, and Smooth

Per my recent column on high-speed designs, you can reduce the need for exotic materials if you have the luxury of keeping the high-speed lines as short as possible. Losses are directly proportional to line length. If a compact design is viable, you can save on both the cost of materials and the consumption of square meters.

### Panelise With Waste Minimisation in Mind

Designing with panel size in mind can save on material costs. The late Martin Cotton was a firm believer in optimising the total design to

Figure 1: Half the length, half the losses.

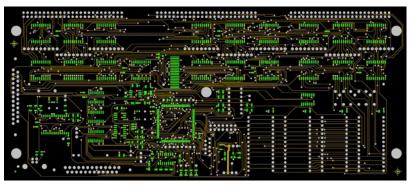

Figure 2: A single PCB.

maximise the use of standard panel size. While panelisation software helps with optimisation, the designer can make life easier for the fabricator by considering the panel size when designing the entire system. It is also worth noting that PCB fabricators have made large strides in optimising panel use and being able to fabricate closer to panel edges.

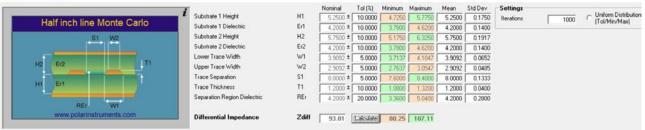

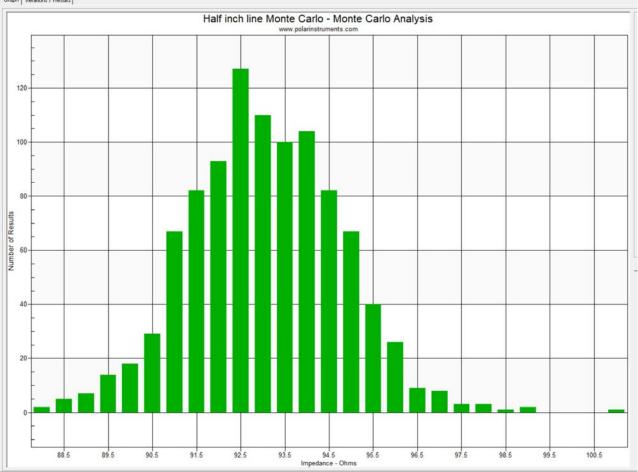

#### **Simulate Where You Can**

Simulation reduces the number of prototype turns and simulates how a design may respond to normal component variation in production. Monte Carlo simulations for electronics design allow you to see how much variation to expect over typical production runs. Monte Carlo tools add a dose of realism to the engineering process, as it's easy to be seduced

by the multi-digit precision of modeling tools and circuit simulators. Tools with the ability to run simulations with expected parametric variations add confidence to the design process and give the designer more confidence in the finished yield, reducing the need to run extensive and expensive physical prototype turns.

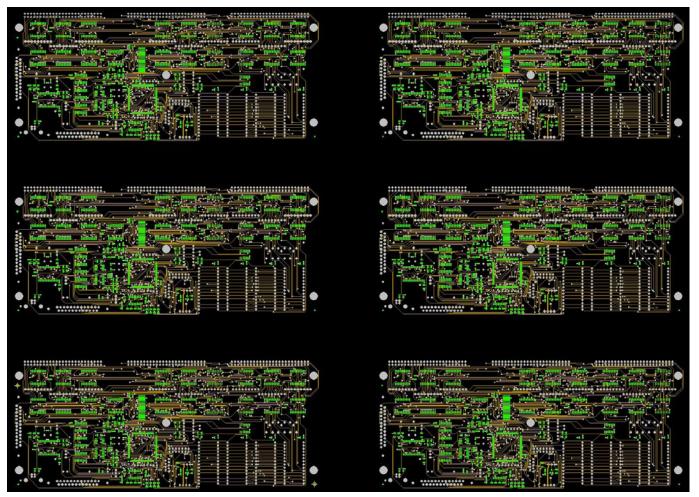

Figure 3: Six up. Panelisation easy with simple shapes, but for more complex outlines, panelisation software tools can increase the board yield per square foot of material.

Figure 4: Running production simulation allows you to see how much window you have for production variation and helps maximise yield.

#### Conclusion

Always keep an open mind and look for cost savings from different angles. My opening note on energy costs is interesting for fabricators because, with energy costs being high, saving energy for the same functionality by choosing an alternate stackup is a win all around. There are many ways to save costs, so it pays to keep your eyes open for innovative solutions. **DESIGN007**

#### References

1. "A parametric approach to quantifying the environmental impact of PCB manufacturing," by Cauwe, Willems, and Geerinckx (IMEC/IMEC/ACB), CMST IMEC Research Group, Ghent University BE.

Martyn Gaudion is managing director of Polar Instruments Ltd. To read past columns, click here. Martyn is the author of *The Printed Circuit Designer's Guide to... Secrets of High-Speed PCBs*, Parts 1 and 2. Hmm... If I have a conductor width and isolation distance of 40 μm (1.5 mils), does that mean my PCB is considered Ultra HDI?

PCBs are complex products which demand a significant amount of time, knowledge and effort to become reliable. As it should be, because they are used in products that we all rely on in our daily life. And we expect them to work. But how do they become reliable? And what determines reliability? Is it the copper thickness, or the IPC Class that decides?

Every day we get questions like those. And we love it. We have more than 600 PCB experts on 3 continents speaking 19 languages at your service. **Regardless where you are or whenever you have a question**, contact us!

#### What's your PCB question?

www.ncabgroup.com/faq-about-printed-circuit-boards/#ask

**Reliable** answers. **Reliable** PCBs.

## **Cost-optimize Your PCB** Design and Specifications

Article by Erik Pedersen and Richard Koensgen, Illustrations by Hervé Chevaleyre ICAPE GROUP

Knowledge is the key to identifying the small details that makes the big cost difference for your printed circuit board. There are many types of printed circuit boards and multiple choices between the development of schematic and BOM to PCB technology selection, electronic PCB design, mechanical and physical properties, and PCB specification.

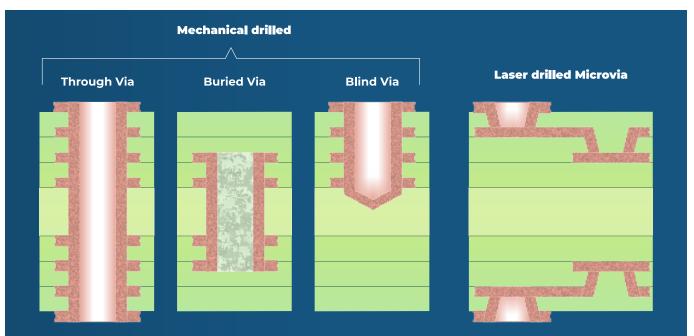

#### **Component Technology and BGA Size**

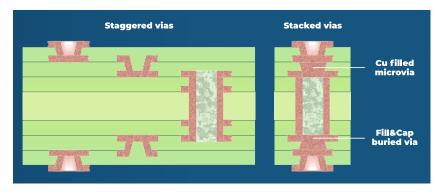

The component size and technology have the most significant influence on the PCB cost. Most surface-mounted microchips can be designed into standard PCBs with plated through-holes. If the same microchip comes in a BGA package, it might need microvias and buried vias using a higher wiring density to be designed into an HDI PCB. Generally, PCBs containing BGAs become HDI PCBs when the ball center-to-center pitch is below 0.8 mm. If your physical board properties allow it and the component availability is equal, you should strive to find the BGA with the largest pitch to reduce the component and PCB cost.

For example, the same BGA microchip can be found with pitch 0.8 mm, 0.6 mm, and 0.5 mm. The 0.8 mm pitch BGA can be routed on an eight-layer standard PCB with a price index of 100. The 0.6 mm pitch can be routed on a (1-6-1) eight-layer, one-step HDI PCB with a price index of 200. The 0.5 mm pitch BGA can be routed on a (2-4B-2) eight-layer, threestep HDI PCB with a price index of 350. The number of lamination steps is the most signifi-

#### autolam: Base-Material Solutions for Automotive Electronics

Automotive electronics technologies are evolving at an increasing rate. Paying attention to the properties of materials at the substrate level is the first step towards achieving the most stringent performance targets of today's automotive manufacturers. autolam offers the solutions demanded by the diverse and unique requirements of automotive applications today and in the future.

#### venteclaminates.com

cant cost driver for HDI and ultra HDI PCBs. Designs with BGAs equal to or less than 0.4 mm and multiple rows challenge the capability of HDI suppliers, which leads to the use of UHDI design parameters and thereby reduces the availability and increases the cost.

#### **Material Selection**

Correct material selection that complies with the performance and functionality of your application also plays a crucial role in the PCB cost.

The most common stackups of standard PCBs are specified with 35  $\mu$ m Cu on all layers. The manufacturer starts on 17.5  $\mu$ m Cu on outer layers and 35  $\mu$ m Cu on inner layers, since the final outer layer Cu thickness reaches approximately 35  $\mu$ m after plating. But 35  $\mu$ m Cu on the inner layers isn't always required and can be replaced by 17.5  $\mu$ m for the current flowing in many electronic devices. This, in turn, lowers costs.

Beyond this, Cu thickness above the standard 35 µm represents a considerable extra cost.

The base material choice depends on the PCB technology used for your application and the performance needed. By specifying a specific brand and type of material, you diminish the supplier availability and often prolong the lead time of the suppliers by adding material purchase time. Seeking advice on the material specification from a specialist like ICAPE can save time and money by ensuring that your choices are based on performance rather than a specific brand and type of material. We recommend specifying the important critical material characteristics for the performance of your application, including glass transition temperature (Tg), coefficient of thermal expansion (CTE), dielectric constant (Dk), dissipation factor (Df), comparative tracking index (CTI), and maximum operating temperature (MOT). Thereby you allow the supplier to provide their offer based upon the most available and cost-optimized material fulfilling your specified criteria.

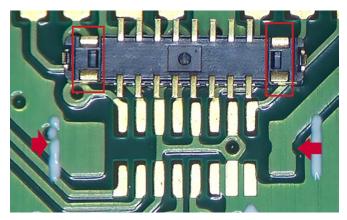

#### **PCB** Thickness and Stackup

Standard stackups contain only one sheet of prepreg in between each conductive layer. Using two or more sheets of prepreg will increase the PCB cost by approximately 2.5-6USD/m<sup>2</sup> per sheet.

The most common PCB thickness is 1.6 mm, but could the thickness be reduced to 1.0 mm or 0.8 mm without compromising the mechanical or electrical performance? Reducing the thickness can provide direct cost savings on the PCB price of 1-2 USD/m<sup>2</sup>, but it also reduces the weight, leading to large cost savings on the

freight and finally, it will reduce the weight of your application.

#### **Panel Design and PCB Separation**

Suppliers use standard-size production panels between 18" x 24" to 21" x 26" but some of the newest factories are increasing to double-size production panels like 28" x 49" to optimize the production cost. Most PCBs are delivered in a customer-defined delivery panel designed to optimize the assembly cost. The optimization of the supplier production panel and the customer-defined delivery panel is very important to minimize material waste.

Panel designs of PCBs with odd shapes can lead to undesired and inefficient material utilization. Engineering of these panel designs using rotated steps and nesting, resembling the old computer game Tetris, will often lead to substantial cost savings.

Rigid PCBs are mostly either milled on a CNC routing machine using a standard routing bit of 2 mm, prepared for depanelization by V-cut scoring, or a combination of both CNC milling and V-cut.

The V-cut is cheaper and faster for both the PCB manufacturers and for the post-assembly depanelization, but it leaves a rough PCB edge, and ceramic components must keep a minimum 2–3 mm board edge safety distance to avoid undesired component stress during the V-cut depanelization.

The depanelization of panels with break-tabs is more time-consuming since every break-tab must be removed by a mechanical cutter or the gentler routing method.

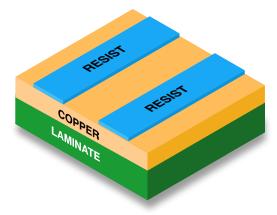

#### PCB Complexity and Design Wiring Density

The component size and wiring density are the main qualifiers of the PCB technology and layer count needed. Design features like minimum trace and space as well as minimum via-hole size limit the supplier range and thereby have a

direct impact on the PCB price.

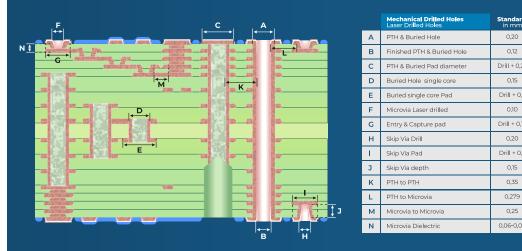

We are often asked specific questions about the cost impact of increasing the number of layers, adding microvia steps, reducing trace width and space, reducing hole sizes, etc.

**Layers vs. price:** Going from two to four layers increases the PCB cost by approximately 50% and for every two layers up to 12 layers will increase the cost by approximately 30%. At higher layer quantities, the percentage increase per extra layer pair declines.

**Standard ML vs. HDI additional microvia steps:** Going from a standard 10-layer PCB to a 10-layer one-step microvia HDI increases the cost by 50–60%. Adding buried vias from layers two to nine and microvias from layers two to three plus eight to nine increases the cost by 100%. Each additional microvia step increases the cost by 100%.

Trace and space: At ICAPE, we recommend that mainstream low-cost products use 6 mil/150  $\mu$ m trace and space since all suppliers will be available, including the really dedicated low-cost suppliers. Reducing the trace and space to 4-mil/100  $\mu$ m may exclude some dedicated low-cost suppliers, increasing the cost. Reducing the trace and space to 3-mil/76  $\mu$ m will further reduce supplier choice and will mainly only be possible for HDI suppliers. Reducing the trace and space to 2-mil/50  $\mu$ m will only allow suppliers with UHDI capability.

**Minimum via hole size and tolerance:** Most suppliers can offer plated through-hole 0.3 mm via-hole size without additional cost. Reducing to 0.2 or 0.25 mm via-hole size may increase

|   | Mechanical Drilled Holes<br>Laser Drilled Holes | Standard<br>in mm | Advanced<br>in mm | Standard<br>in mil | Advanced<br>in mil |

|---|-------------------------------------------------|-------------------|-------------------|--------------------|--------------------|

| А | PTH & Buried Hole                               | 0,20              | 0,15              | 8                  | 6                  |

| в | Finished PTH & Buried Hole                      | 0,12              | 0,07              | 5                  | 3                  |

| С | PTH & Buried Pad diameter                       | Drill + 0,25      | Drill + 0,15      | Drill + 10         | Drill + 6          |

| D | Buried Hole single core                         | 0,15              | 0,10              | 6                  | 4                  |

| Е | Buried single core Pad                          | Drill + 0,2       | Drill + 0,12      | Drill + 8          | Drill + 5          |

| F | Microvia Laser drilled                          | 0,10              | 0,06              | 4                  | 2,36               |

| G | Entry & Capture pad                             | Drill + 0,15      | Drill + 0,12      | Drill + 6          | Drill + 5          |

| н | Skip Via Drill                                  | 0,20              | 0,15              | 8                  | 6                  |

| 1 | Skip Via Pad                                    | Drill + 0,2       | Drill + 0,18      | Drill + 8          | Drill + 7          |

| J | Skip Via depth                                  | 0,15              | 0,2               | 6                  | 8                  |

| к | PTH to PTH                                      | 0,35              | 0,3               | 14                 | 12                 |

| L | PTH to Microvia                                 | 0,279             | 0,228             | 11                 | 9                  |

| м | Microvia to Microvia                            | 0,25              | 0,15              | 10                 | 6                  |

| Ν | Microvia Dielectric                             | 0,06-0,08         | 0,10              | 2,36-3,15          | 4                  |

the cost by 5-6 USD/m<sup>2</sup>. Going below plated through-hole 0.2 mm via-hole size is only recommended on PCB thickness less than 1 mm and it will increase the price significantly. The common finished tolerance on plated throughholes is  $\pm 0.1$  mm; tighter tolerances may require a change to a more sophisticated surface finish.

Additional expensive processes:

- Peelable mask and Kapton tape

- Hard gold

- Edge plating and plated half holes

- Plated through-hole copper requirements beyond IPC Class 3

- Back-drilling

- Countersink holes

- Via filling IPC type 5, 6, and 7

#### **Surface Finish**

The surface treatment must comply with the component choice, but it is important to consider the price implications of your choices. The main surface treatments based on price are: OSP, LF HASL, immersion Sn, immersion Ag, ENIG, and ENEPIG.

The surface treatment percentage influence on the price depends on the PCB cost driven by the technology, layer count, and board complexity.

On a two-layer PCB, the surface finish using LF HASL would represent 8% of the total cost.

On the same PCB using ENIG, the surface finish would represent 30% of the total cost. On a 10-layer PCB, the surface finish using LF HASL would represent 2.5% of the total cost. On the same PCB using ENIG, the surface finish would represent 9% of the total cost.

The relation of the PCB costs to the surface finish and assembly technology of components can result in considerable cost savings, which you can easily use to your advantage.

#### Summary

The cost structure varies between suppliers, and it is difficult for PCB developers and designers to predict the most cost-optimized design and PCB specification. Having an experienced partner like ICAPE Group is your easiest pathway to extensive PCB-technology knowledge and related cost impacts. DESIGN007

#### Sponsored link: www.icape-group.com

Erik Pedersen is FAE and quality director at ICAPE Group.

Richard Koensgen is a field application engineer at ICAPE Group.

# LOOK WHO'S TALKING, TOO!

# My Anti-venom to PCB Cost Adders

#### **Target Condition**

Feature Column by Kelly Dack, CIT, CID+

As a kid, I remember long, hot, cross-country trips to the Midwest with my grandparents to visit relatives. Riding in the backseat of a 1970s station wagon without air conditioning, the only thing I had to look forward to was stopping at Stuckey's in Oklahoma, which had a snake farm right next door. As luck would have it, after a hundred miles of passing signs advertising "Ramona's Snake Farm," Grandpa pulled in and made my trip come alive. I'd never seen a poisonous snake up close, and there were hundreds of them.

Snake pits, snake handlers, and venommilking demonstrations garnered lots of oohs, ahs, and applause from the motor-tourists, including me. The handlers explained the snakes' habitats and unique characteristics and, most importantly, how to avoid getting bit. I left the snake farm with a greater understanding of snakes, and I'm proud to say I've never been bit.

One fairly benign species is *Vipera berus*, known as the common European adder, a venomous snake that isn't particularly aggressive, nor is its bite fatal. However, PCB designers risk getting bit by "adders" of another kind: *Serpens addit nimium pretium*, or simply, cost adders. Often coiled up in product development teams' brainstorming sessions or lurking inside the unexplored settings of our PCB design tools, these dangerous critters are of the profit-killing species.

In my walkabouts through the PCB design and manufacturing jungles, I've met many PCB designers who have suffered painful bites from these cost adders. These critters are particularly

### Don't Skip a Beat

#### QUICK TURN RF, MICROWAVE, ANTENNA EXPERTS

Accurate Circuit Engineering 3019 Kilson Drive Santa Ana, CA 92707 (714) 546-2162 • sales@ace-pcb.com For technical assistance call: James Hofer (714) 425-8950 www.ace-pcb.com

dangerous when a PCB designer steps naively into unfamiliar areas and does not know where to look. I have been bitten many times by the cost adder, but I've learned from my mistakes.

Now, I'm offering a few free doses of cost adder anti-venom.

#### Species: *Serpens Materia* (Material Cost Adders)

While most think of PCB material as simple glass-epoxy sheet stock or FR-4, PCB laminates have expanded into very advanced, brandname, trademarked product lines that target specific performance and operational requirements for advanced PCBs.

When a PCB design layout goes to production, be wary of Serpens materia. Fabrication drawing notes must contain a material specification through which the PCB is made. Global PCB fabrication suppliers prefer simple glass/ resin or polyimide laminates that can be readily procured from multiple sources. But often, PCB designers make the mistake of specifying brand-name materials or part numbers when it is not required. Other designers even declare "no substitutions." Designers who proceed in this manner without advanced understanding and justification are reaching dangerously into the den of Serpens materia. When their design moves to volume quantities, they will most certainly experience a painful strike from this adder with swelling of cost and necrotic product profit margin to follow.

The anti-venom for *Serpens materia* is modest but powerful. It must be injected directly into the design fabrication note-specifying material. After dosing, a basic material note's brand name, cost swollen specification can heal by stating: "Materials: Laminated, glass base, epoxy resin type FR-4 series or equivalent per IPC-4101 with Tg >/= 130°C and a Td >/= 300°C electro-deposited copper foil. Nominal base (starting) copper thickness for all layers shown on stackup detail."

#### Species: Serpens Processus (Process Cost Adders)

There are many ways to process a single feature on a PCB. For example, a board edge can be routed out, punched out, V-scored, laser cut, or even cut with an abrasive water jet. The way the designer lays out the shape of the board geometry will allow or eliminate many of the available processes. If a board outline maintains a rectangular shape, it can tolerate almost any process and allows the supplier to use V-scoring, which can be very cost-effective.

But rounding the corners to eliminate a sharp edge means an additional process step of routing to form the rounded edge. With rounded corners and straight edges, a PCB can be processed with a combination of V-scoring and routing at a cost for the additional process. Rounded features on a PCB outline are notorious hiding places for *Serpens processus* because of the additional process of routing and associated machine time or shifting the processing to a tab-route solution requiring mouse bites.

Mouse bites can cause localized stress on the PCB edge and lead to component cracking. *Serpens processus* is a wily species, often cohabiting with other, beneficial process species. To avoid being bitten, designers must focus on design constraints, keep them simple, and be aware of design features that add processing. Common lairs for process cost adders are PCB outlines, hole definitions, unique sizing, finishing, or coatings, especially ones requiring extended cure times.

The anti-venom is applied topically and serves mostly as a repellent; PCB designers must apply heavily during times of early project planning and treat fellow stakeholders who might be unaware of the dangers. Signs of an early bite, however, will materialize via stakeholder team suggestions describing oversized, curvy-shaped PCB designs with both plated and unplated countersunk mounting holes. In rare cases, wild visions of PCB stackups capable of carrying 80 amps and running down an ordinary soldering line must be treated immediately. In these cases, the venom of the process cost-adder has reached the brain tissue of this stakeholder and must be stopped before reaching the project budget and swelling it until it pops.

#### Species: *Serpens Apparatus* (Machinery and Equipment Cost Adders)

The safest way to avoid the bite of Serpens apparatus is to stay on the high ground, making quick hops between the machine stations that do the work of manufacturing the PCB. If a designer can clearly see and understand what it takes to hop to the next machine station without falling adder-infested to the jungle floor, the chances of being bitten by Serpens apparatus decrease greatly. But many PCB

designers fail to study the equipment and capabilities of the fab and EMS providers, relying only on the PCB design software as a GPS guide.

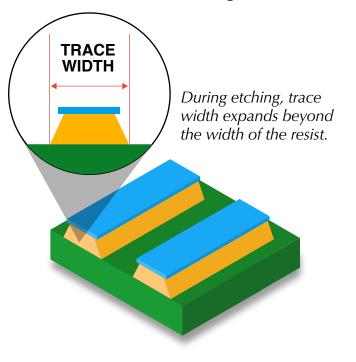

We see news stories about travelers not researching their destination and winding up in dangerous situations by relying solely on GPS. Unfortunately, designers often suffer the same metaphorical fate. PCB design software can convert almost any geometric feature into a process machine language. Via padstacks are not only identified as drilled and plated holes, but our layout tools now invite designers to select from several filling and capping options without identifying the added cost or equipment needed.

Just last week, I had to rescue a designer who had fallen to the jungle floor in this manner. He'd pressed some via definition buttons and unknowingly stirred up a nest of *Serpens apparatus*. In the nick of time, I yelled, "Cost adder, watch out!" Once we scrambled back up on the DFM observation platform for a design review,

we could clearly scope out the equipment that would have been required for

the unnecessary filled and capped vias. We were lucky enough to avoid being bitten by *Serpens apparatus* and lived to tell the story.

The anti-venom for *Serpens apparatus* does not yet exist. The best prevention for this type of bite involves traveling to PCB design and manufactur-

ing trade shows and taking frequent tours of PCB and EMS manufacturing facilities. There is simply no better way to get in touch with the equipment and the people who run it. To remain above the manufacturing jungle canopy and to know where to jump next, PCB designers must become familiar with the following equipment and their respective capabilities and design requirements:

- Drilling machines

- Photoimaging equipment

- Plating and etching tanks

- Wet coating machines

- Laser direct imaging machines

- Printing machines

- Flying probe test equipment

- Solder printing machines

- Pick-and-place equipment

- Conveyers and pallets

- Reflow ovens, wave and selective soldering equipment

- Optical inspection equipment

- Routing, nibbling, and v-scoring equipment

- Functional and in-circuit test equipment

#### **Know Your Cost Adder Species**

As PCB designers, we cannot wander blindly and naively within our PCB design layout tools—clicking buttons and assigning values without the ability to count the cost of such actions. Whenever we guess what is needed to form a PCB feature without understanding, we are, in effect, sticking our appendages into the cost adder's den. If you're like me, you are a PCB designer who learns in person. You need to get a tactile understanding of the subject matter at hand. To educate yourself with the excitement of a kid in a snake farm, you need to make every effort to tour a PCB manufacturing facility and/or attend a trade show displaying lots of materials, processes, and equipment. There, you can safely wander the aisles and view many PCB manufacturing cost equivalents to rattlesnakes, water moccasins, vipers, and all the various types of adders safely behind the glass or yellow lines painted on the concrete floors.

Before it's too late, slowly and cautiously step away from your PCB design laptops. Do not make any sudden moves. Turn and run to the closest PCB manufacturer or trade show to learn more about what it takes to keep PCB project costs low. **DESIGN007**

Kelly Dack, CIT, CID+, provides DFx centered PCB design and manufacturing liaison expertise for a dynamic EMS provider in the Pacific Northwest while also serving as an IPC design certification instructor (CID) for EPTAC.

To read past columns, click here.

#### **BOOK EXCERPT**

### The Printed Circuit Designer's Guide to... DFM Essentials

#### **Chapter 10: Cost Driver Summary**

#### Low-cost Adders (<10% board cost)

Complex routing and scoring mean a small increase in process time, but a process is still required which will be driven by NC programming; it may limit tool life as a function of diameter. Thicker or thinner PCBs (>0.093" [0.229 mm], <0.030" [0.762 mm]) means a material cost variation but it is minimal. Via plug or button print requires a small process change to the screen-print mask dot.

#### Medium-cost Adders (10–25%)

Regarding drilled hole quantity, there is a cost adder for high-density design-driven hole count and process time. With smaller drilled hole size, the small drill diameter (<0.010" [0.254 mm]) limits throughput and stack height. Embedded resistors with Ohmega/Ticer technology will need additional core testing and finished board verification. Non-FR-4 materials, like PTFEs, can be 10 to 20 times the FR-4 cost, and material cost is generally 25–50% of the board cost. Edge plating will have additional processes required prior to plating.

#### High-cost Adders (>25% board cost)

Advanced technologies may become "science projects" with industry non-standard processing or materials, or "bleeding edge" technology (<0.003" [0.076 mm] L/S, 1:1 aspect ratio microvias, 0.4 mm BGA technology, etc.). Sequential lamination and complex via structures, as well as metal core or external heat sink requirements, also add cost.

If layer count will be >30 layers, the yield impact can be significant. Combination/hybrid material sets can be high-cost adders. Regarding material/panel utilization, test coupons and board size can greatly reduce panel utilization; array configurations reduce panel utilization with unusable real estate; and there may be limited availability of panel sizes.

Selective plating means multiple surface finishes or multiple thicknesses, complex processing requirements (e.g., masking), and the yield risk of combining non-standard processes. There are also

cost adders for line width and spacing below industry standards for any given copper weight:

- ½-ounce copper: 0.003"/0.003" (0.076 mm x 0.076 mm)

- 1-ounce copper: 0.004"/0.004" (0.102 mm x 0.102 mm)

- Ultra-high-density interconnects

- Sub 1 mil line/space (25 and 15 micron)

Understanding the cost drivers in PCB fabrication and early engagement between designer and fabricator are crucial elements that lead to cost-effective design success.

This chapter was extracted from the newly published book, The Printed Circuit Designer's Guide to DFM Essentials, now available free from the I-Connect007 library.

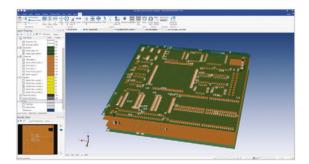

## Impact of the Altium-Ansys Partnership on PCB Design

Article by Josh Moore

There's a saying in electronics hardware design: "There are two types of electronics designers: those who have signal integrity problems and those who will." This adage emphasizes the inevitability of encountering and the need to address signal integrity (SI) and power integrity (PI) issues.