# NOVEMBER 2023

# Your guides to success.

Want to up your game in about 30 minutes? Written by industry experts, all our books contain knowledge that you can apply immediately to make you (and your company) more succesful.

"I-007ebooks are like water in the desert ...it's up to you to drink it in order to survive!"

> Stephen V. Chavez Senior Product Marketing Manager Siemens

# **BOOKMARK OUR LIBRARY**

# **A Distinct Evolution from DFM**

# "In an industry racing against time, MDD is the key to staying ahead."

Ammar Abusham DFM Integration Engineer (AR EE Team) Meta Reality Labs

### **NOVEMBER 2023 • FEATURE CONTENTS**

# Simplfication

In this month's issue, our expert contributors explain how to design PCBs without making them complex and over-constrained—whatever the level of technology. We also discuss the effect your decisions and tradeoffs have on design complexity, as well as the need to thoroughly understand how electrical and manufacturing limitations can lead to over-constraining your board.

FEATURE ARTICLES

22 Your Thermal Designs Are Inefficient by Doug Brooks and Johannes Adam

30 8 Simple Rules for Streamlining Your Design by Chris Young

36 Avoid the 'Ferrari Problem' and Simplify Your PCB Design by Zach Peterson

### FEATURE INTERVIEW

**10** Simplifying Your Design: An Overview with Kris Moyer

### FEATURE COLUMNS

- 16 Simplest Stackups Specified by Martyn Gaudion

- 46 Take It From Scotty: Simple Really Is Better by Tim Haag

66 The Simplest Way Is the Best Way by Joe Fjelstad

# Don't Skip a Beat

## QUICK TURN RF, MICROWAVE, ANTENNA EXPERTS

Accurate Circuit Engineering 3019 Kilson Drive Santa Ana, CA 92707 (714) 546-2162 • sales@ace-pcb.com For technical assistance call: James Hofer (714) 425-8950 www.ace-pcb.com

### **NOVEMBER 2023** • ADDITIONAL CONTENTS

# DESIGNOOT

### SHORTS

- 9 Processing Quantum Information Reliability

- 14 Q2 Revenue for Top 10 IC Houses Surges by 12.5%

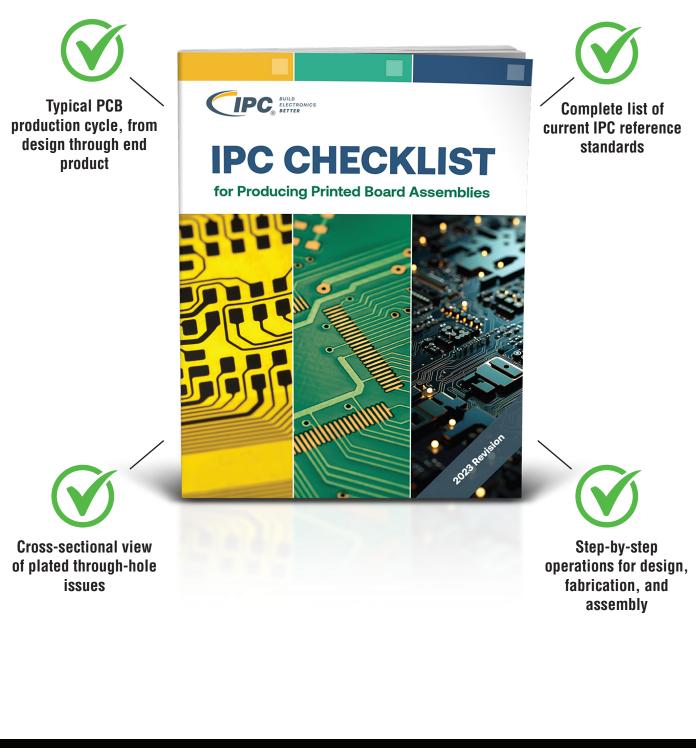

- **35** Infographic: Anatomy of IPC Checklist

- **39** Brandy Tharp: A Passion for Helping Others

- 63 Accelerating Battery Research With Robots

### COLUMNS

- 8 Simply Speaking by Andy Shaughnessy

- 40 Best Practices for Ensuring PCB Design Manufacturability by Matt Stevenson

52 Just a Matter of Time by Barry Olney

### INTERVIEW

60 Talking UHDI With John Johnson, Part 1 by Steve Williams

### HIGHLIGHTS

- 28 MilAero007

- 64 Flex007

- 72 Top Ten Editor's Picks

### DEPARTMENTS

- **75** Career Opportunities

- 84 Educational Resources

- 85 Advertiser Index & Masthead

### **6** DESIGNO07 MAGAZINE I NOVEMBER 2023

# autolam: Base-Material Solutions for Automotive Electronics

Automotive electronics technologies are evolving at an increasing rate. Paying attention to the properties of materials at the substrate level is the first step towards achieving the most stringent performance targets of today's automotive manufacturers. autolam offers the solutions demanded by the diverse and unique requirements of automotive applications today and in the future.

### venteclaminates.com

# Simply Speaking

# **The Shaughnessy Report**

by Andy Shaughnessy, I-CONNECT007

During a recent trade show, a group of us were wondering how much money and labor is wasted annually because of PCB designs that are over-constrained or otherwise needlessly complex. It had to be millions of dollars, or maybe even tens of millions.

Like a lot of long-running challenges in PCB design, this issue didn't pop up overnight. It's not like anyone wants to make their designs more complicated than is necessary. As we'll

see in this month's issue, this happens for a variety of reasons, such as increasing signal speeds, faster rise and fall times, and shrinking silicon technologies.

If your documentation template is too constrained, but the system has been in place for years, you may have already spent hundreds of thousands of dollars in extra fab costs and wasted labor resources, along with jobs put on hold unnecessarily.

Some designers over-constrain their entire boards when only a handful of features actually require tight tolerances. Every dimension specifically called out is bought and paid for, because it has to be inspected, and that can be an expensive habit.

So, in this issue, our expert contributors explain how to design PCBs without making them complex and over-constrained—whatever the level of technology. We also discuss the effect your decisions and tradeoffs have on design complexity, as well as the need to thoroughly understand how electrical and manufacturing limitations can lead to overconstraining your board.

We start off with a conversation with Kris Moyer, who explains why "one size fits all" is not a great plan for setting board constraints. Next, Martyn Gaudion discusses various ways to design the simplest—and best—stackup possible. Doug Brooks and Johannes Adam tell us why thermal vias are usually ineffective at dissipating heat, but do a great job of blocking potential routing channels. Chris Young has a great set of guidelines called "8 Simple Rules for Streamlining Your Design."

Zach Peterson explains why designers should stop designing PCBs like Ferraris, the famously complex Italian supercars. Tim Haag describes why designers should follow the lead of "Star Trek's" Montgomery "Scotty" Scott and keep their designs simple, and Joe Fjelstad points out why the simplest design is usually the best. We also have columns by Matt Stevenson and Barry Olney, and Steve Williams has a conversation with American Standard Circuit's John Johnson on UHDI.

Trade show season is here, and we'll be covering productronica next week. **DESIGN007**

Andy Shaughnessy is managing editor of *Design007 Magazine*. He has been covering PCB design for 23 years. To read past columns, click here.

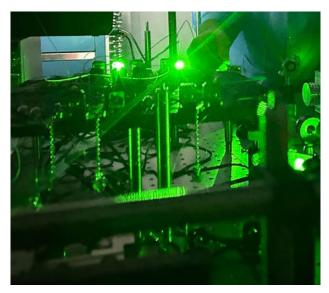

# Processing Quantum Information Reliably

Using laser light, researchers have developed the most robust method currently known to control individual qubits made of the chemical element barium. The ability to reliably control a qubit is an important achievement for realizing future functional quantum computers.

This new method, developed at the University of Waterloo's Institute for Quantum Computing (IQC), uses a small glass waveguide to separate laser beams and focus them four microns apart, about four-hundredths of the width of a single human hair.

The researchers created a waveguide chip that divides a single laser beam into 16 different channels of light. Each channel is then directed into individual optical fibre-based modulators which independently provide agile control over each laser beam's intensity, frequency, and phase. The laser beams are then focused down to their small spacing using a series of optical lenses similar to a telescope. The researchers confirmed each laser beam's focus and control by measuring them with precise camera sensors.

The new waveguide method demonstrates a simple and precise method of control, showing promise for manipulating ions to encode and process quantum data and for implementation in quantum simulation and computing.

(Source: University of Waterloo)

Feature Interview by the I-Connect007 Editorial Team

It's safe to say that millions of dollars, not to mention man-hours, are wasted each year because of over-constrained, overly complicated PCB designs. Much of this is due to the increase in signal speeds and rise times, even in "mature" PCBs, and the extra cost is already part of the budget.

For this issue on simplifying PCB designs, the I-Connect007 Editorial Team spoke with IPC instructor Kris Moyer about ways that designers can avoid overconstraining their designs and making them needlessly complex. As Kris says, streamlining your design comes down to having a solid understanding of fab and assembly processes and the silicon tradeoffs that can simplify or overcomplicate your design, as well as the need to start working with fabricators early in the cycle.

### Andy Shaughnessy: What are some typical snafus and missteps that you see designers make to overcomplicate their designs?

*Kris Moyer:* Here's what often happens: Let's say you have one connector on your board that needs tight tolerance. But rather than dimensioning to just that connector, locally, designers will do a tight tolerance to the data from the global dimensioning system, which now constrains the entire board.

Or, if they need perfect coplanarity on a BGA part for good BGA mounting, they'll put co-planarity back over the entire board where they don't need it, because regular chips, gullwings, and so on don't need the same amount of coplanarity as a BGA—or they'll try to hold layer tolerances: "I need a 2-mil layer plus or minus 10%," because they know that 10% is

# AMITRON FACTORY 5.0 Manufacturing for the future.

# Automation

Gather data from equipment and processed into a central data storage platform.

# Procedures

Machine learning (AI) and operational procedures to handle data and processes.

**People** Teach and train people how to react to changes in processes in real time.

# **LEARN MORE ABOUT FACTORY 5.0**

www.amitron.com | (847) 290-9800 support@amitron.com

CHECK OUT

FACING THE

FUTUR

normal for tolerance, but they missed the part of the spec that says 10% or 1 mil, whichever is greater. Fabricators can't hold that tight a layer-to-layer tolerance when it's below a certain layer thickness.

Below about a 10-mil thickness, the best fabricators can do layer-to-layer is 1 mil for nominal processing. If you want to hold a tighter tolerance, you're paying for 100 to get five boards. That's just a couple of examples. Another is overly tight hole tolerances: "I want to have 150-mil diameter hole plus or minus one mil." Again, it's unreasonable, right?

At several companies where I've worked or consulted, they still have mechanical engineers do the documentation for the boards. So, the board designer designs the board and passes

it over to let the ME do the documentation and follow their standard documentation template. But the designers don't realize that a machine shop that's milling a chunk of aluminum can absolutely hold plus or minus 1 or 2 mils of tolerance.

There's not a lot of understanding of what the manufacturing capabilities are. They tried to hold the manufacturing nuances that they're used to in mechanical engineering, apply those to board design and board manufacturing, and find themselves overly constrained.

### Shaughnessy: How did the MEs end up in this position?

Moyer: If you go back to the early days of CAD tools, the MCAD tools were set up from day one to create good documentation packages. The ECAD tools would output a document, but it didn't have good documentation capabilities like GDT control frames. In early ECAD tools, if you had 3D at all, it was simple extruded rectangles. "Here, put a box on your board where your part is extruded up, so you know what the thickness is." That represented your part,

with the other stakeholders-the EEs, MEs, managers, and so on. You have to be able to say, The solution is to learn the standards and

learn the manufacturing

processes.

and so on.

"I understand where you're coming from. However, this is the manufacturing limitation. If you spec it this way, it's a big cost-adder to the board. But if we document it this way, we will get the same effect that we want,

but now we've simplified

our board design and constrained it just enough for what we need without overconstraining."

whereas the MEs had full 3D modeling to build

very complex, realistic structures, so they can

do all of that. A lot of companies just said, "You know what? Just send the board to the ME."

They already had a template defined and the

ME could do all of these little detailed views

*Moyer*: The solution is to learn the standards

and learn the manufacturing processes. Take

all the IPC training classes that you can to learn

these processing capabilities and where the limitations are. Then the board designer can

have intelligent, knowledgeable discussions

Shaughnessy: What's the solution here?

Happy Holden: Andy, I think what's complicating the idea of simplifying your design is that BGAs and other part miniaturization and the shrinking pitch of connections all sneak up on designers. A lot of times, they design the whole board and get everything connected except for the last 5%. Then they run into via starvation, and they're forced to go with laserdrilled blind vias. I can always tell that, if it's a complex board with 127 laser-drilled blind vias, that's a clear indication that the designer never intended this to be an HDI board. He didn't know about the simple models they can use that would have told him ahead of time that the size of the board, the pitch that he's working with, and the netlist indicates that this will require HDI. Instead of using 127 vias, you should have used 5,000 microvias, because that would have reduced the layer count and everything else. But now, he's all the way through the design, and he's got via starvation.

People mistakenly believe that HDI costs too much. Well, HDI costs too much because designers don't know how to use it, and they've never been properly trained that if you go with blind or buried vias, then you have to start out from the very beginning and use one of the models to indicate how many signal layers you'll need.

# Shaughnessy: This sort of thing is in the IPC standards, so familiarity with the standards would definitely go a long way.

*Holden:* Oh, yes, absolutely. That's why we wrote the first HDI Design Guide, which is not a standard. We included some of the different density modeling equations so that before you ever start, do some of these equations to see whether you will need blind and buried vias. If you think you will do HDI without it, then you will get trapped at the very end of the process, and it will be expensive.

Moyer: I will give you a perfect example. I recently consulted with a company that builds products that go in one direction really, really fast and don't come back. They had designed a coplanar transformer for their board, which was rigid-flex, using their magnetics software. Their magnetics software said that the arc here should be this wide, and you should have this much gap to the next arc, and so on. All was good. They said that to carry this much current, it should be this thick. From a purely theoretical physics point of view, everything they did was correct. What they came up with was a coil transformer design, set to adjacent layers, so you'd have primary and secondary. The traces were 5 mils wide with 4-mil spaces, and they designed it out of three-ounce copper.

Kris Moyer

This was physically impossible to build. With three-ounce copper, you need at least 10 to 15 mils of gap between traces. The narrowest copper feature that most fabricators will touch is about 10 mils, but they prefer about 12 mils with three-ounce copper. The software that the engineers used gave them some numbers and they designed the whole thing, and they could not get a fab shop anywhere in the world to touch this. I told them what they needed to do to change it, but they didn't listen to me, so I stopped consulting with them.

### Shaughnessy: So, there are probably hundreds of ways that a board can be made overly complex.

*Moyer*: The fun thing about a printed circuit board is that you can overconstrain it and overdesign it and it will still work. But my favorite question is, "What's the definition of optimal design?" That's really difficult to answer, because given a bill of material and a schematic, there's an almost infinite number of ways that the board can be physically designed. On the board side, we tend to be over-constrained and on the assembly side, we tend to be under-constrained, so we need to find a happy medium. One thing I see in assembly is that the board designer does not often consider the mechanical side of the design. Assembly requires access for tools, and so on. Fortunately, IPC standards such as the 6012s cover both fab and assembly, if designers actually read them.

### Shaughnessy: I've heard SI engineers halfjokingly say that signals should be as dirty as they can be and still pass margin, because of all the over-constraining going on in high speed.

*Moyer*: Well, yes. But unfortunately, there is a caveat to that. I agree about designing it just enough to pass margin. The problem is not the board designer; it's the silicon designers who keep shrinking silicon technology and silicon geometry.

Now we have chips coming out with edge rates on the order of 100 picoseconds, or even faster. In order to achieve those kinds of square edges to pass the timing, even my digital traces, I now have frequency content up into the gigahertz range, which is approaching RF geometry. I have to worry about insertion losses, emissivity, and susceptibility and all of these RF-level issues, which never used to be a thing. It's insane, and the board designer has zero control over it.

# Shaughnessy: Is there else anything you'd like to add?

*Moyer*: Number one, learn the IPC standards, whether it's through taking classes or just getting hold of standards and reading them yourself. I teach some of these IPC classes (for a little shameless plug here). Also, talk to your fabricator. Don't be afraid to call your fabricator and have those kinds of technical discussions: "Hey, I've got this challenge on my design. Do you have any suggestions?" Your fab might have some recommendations that you never thought about that could be implemented in a much more cost-effective manner than the way you're thinking about doing. I tell my students that all the time, "Your fabricator is your friend."

Shaughnessy: This has been really good. Thanks for your time, Kris. Holden: Very interesting, Kris.

Moyer: Always a pleasure, Happy. DESIGN007

# Q2 Revenue for Top 10 IC Houses Surges by 12.5%

Fueled by an Al-driven inventory stocking frenzy across the supply chain, TrendForce reveals that Q2 revenue for the top 10 global IC design powerhouses soared to US \$38.1 billion, marking a 12.5% quarterly increase. In this rising tide, NVIDIA seized the crown, officially dethroning Qualcomm as the world's premier IC design house, while the remainder of the leaderboard remained stable.

NVIDIA is reaping the rewards of a global transformation. Bolstered by the global demand from CSPs, internet behemoths, and enterprises diving into generative AI and large language models, NVIDIA's data center revenue skyrocketed by a whopping 105%. A deluge of shipments, including the likes of their advanced Hopper and Ampere architecture HGX systems and the high-performing InfinBand, played a pivotal role.

AMD's Q2 performance plateaued at about \$5.36 billion, weighed down by a slump in gaming GPU sales and its embedded segment operations. Conversely, MediaTek, after several quarters of inventory recalibration, witnessed a resurgence with components like TV SoCs and Wi-Fi stabilizing.

Peering into Q3, while inventory levels across companies paint a rosier picture than H1, a pervasive end-user demand slump urges caution. However, a silver lining emerges with CSPs, internet titans, and private firms flocking to generative AI and large language models.

(Source: TrendForce)

# Companionship at its Best

This sequel to Ventec's book series on Thermal Management describes the applications, IMS products and support services to help you understand and overcome thermal management challenges.

# 1·0072Books

# Simplest Stackups Specified

# The Pulse

Feature Column by Martyn Gaudion, POLAR INSTRUMENTS

*"Everything should be made as simple as possible, but not simpler."* —Albert Einstein

Einstein advocated for describing complex theory in the simplest way possible, but not so simplified that key information is lost. We often see this when the media is criticised for "dumbing down" information. However, from an engineering perspective, if a design can be engineered to perform the required application in a simpler or more economical way, then simplification is truly a valuable goal.

## But in the Real World

Often, complex solutions are the only way to realize a design. In these circumstances, the information surrounding a design should be as clear as possible for the people who interact with it during the product's design and lifecycle.

# **Small Is Beautiful**

It's also simpler where signal integrity is concerned. Signal integrity becomes more challenging when interconnects are long in comparison to the rise time or maximum frequency component of the signals you are handling. If you keep your traces short enough, then reflections or impedance mismatch become a nonissue; they still exist but the effects are too small to cause trauma to your signals.

For GHz designs, where loss becomes even more of a concern than reflections, the "keeping it short makes it simple" mantra also holds

# ALL YOUR FLEXIBLE SOLUTIONS

CatheterFlex™

Twenty Layer Rigid Flex

Flexible circuit solutions Rigid flex solutions CatheterFlex® solutions Flexible heater solutions <u>And assembly sol</u>utions too!

And, Assembly Too!

**All Flex Solutions** 1601 Cannon Lane Northfield, MN 55057

(507) 663-7162 AllFlexInc.com

true. With insertion losses being directly proportional to the line length, then halving your line lengths (where possible) will halve your losses: simple and free. I sometimes see questions about line impedance on very short lines, where the frequency of interest is relatively low, and the interconnect at each end of the line is a significant portion of the length. It pays to check whether impedance or loss is an issue in these circumstances. There is a simple Microsoft Excel tool called a critical trace length calculator, which helps check the critical length.

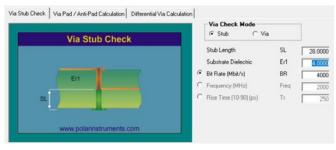

Whilst on the subject of small or short, moving from the X-Y to the Z-axis, the same is true for vias: Keep them short. If you can't keep them short, keep the stubs short. Let's drill down (sorry) on all the possibilities for minimising the signal integrity challenges of vias. Remember that, in most cases, the vias are short compared with the trace length unless it is a really thick board.

Thinner boards (where possible) have inherently shorter vias. Where the PCB is necessarily thick because of high layer count, there are several approaches:

- Minimise the stub length

- Use microvias

- Back-drill the offending stubs

Why are via stubs a problem? Simply put, it is because a signal arriving as a stub sees it electrically twice as long as it is mechanically. A signal arriving from the top layer of the PCB traversing down the via to a trace on an inner layer can't tell the difference between propagating further down the via (the stub) or continuing along the trace, so it does both-the part propagating along the intended trace continues unimpeded. But the part of the signal that chances to propagate down the stub finds an open circuit at the end of the stub and 100% of that diverted signal will reflect and rejoin the main trace, at which point part of the stub reflection will return toward the source and the rest will rejoin the signal headed toward its intended destination. Using buried vias, backdrilling the stub, or using microvias are all technical solutions to this, but an alternative is to (where possible) route so that the stubs are as short as possible—say, on a 10-layer board route a signal from L3 to L8 rather than L1 to L5, which would leave a far longer stub. Sometimes a rapid check to see whether a feature, such as a stub, is a cause for concern can rapidly put you at ease or flag if more attention is needed. Figures 1, 2, and 3 depict differing stub lengths and their relative impact, from "safe to ignore" (green 28-mil stub) to "do something about it" (red 200-mil stub) when the stubs are in a 4Gbit/s data channel.

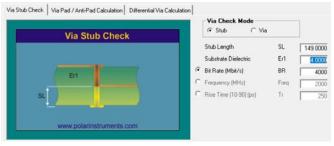

Figure 1: Via length of 28 mils causes no concern at 4 Gbit/s data rate.

Figure 2: Via length of 149 mils causes some concern at 4 Gbit/s data rate.

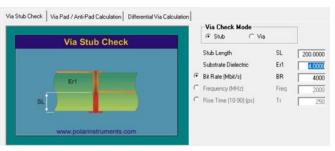

Figure 3: Via length of 200 mils requires attention at 4 Gbit/s data rate. (Find the math behind this in "Signal and Power Integrity Simplified" by Dr. Eric Bogatin)

# **Focused on Flex**

# LaserµFlex series

schmoll

The versatility and precision of laser processing makes it the ideal tool for machining a wide range of materials.

optronics

**Typical applications:**

- Polymer cover foil

- Covered polymer laminates

- Thin, rigid-flex materials

- Inner layers and prepregs

- Separation or decap from tracks

- Structuring cavities

- Microvia and through-hole drilling

For more information call us: +1 (336) 660-2701

burkleamerica.com

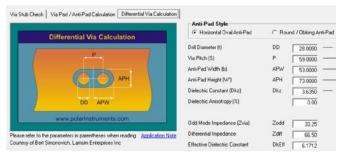

## Modelling Single-ended and Differential Via

Modelling vias is one of the most frequently searched terms driving traffic to the Polar website. One of the counterintuitive points on via modelling is that it is easier to obtain an estimation of a differential via's characteristics than that of a single-ended via. Why? Because differential vias are inherently an out-andreturn path, there are no discontinuities in the return path (or at least they are minor) compared with single-ended vias. This is a key advantage for designs with

ultra high-speed digital signaling in making them easier to design. While you can model a single-ended via with a 3D solver, it only goes to prove the design is compromised. To get the best signal integrity for a single-ended via, it can be necessary to place it next to a ground via which spans all the intermediate planes. Plane pairs to single-ended vias act as slot antennae and cause reflections out and back to the edge of the board. Transitioning a signal from L1 to L3 with a ground on L2 would minimize this, but at same time, you have to check that the stub is still short enough not to be troublesome.

Figure 4: Differential via property calculation, Polar Si9000e. (Courtesy: Bert Simonovich Lamsim Enterprises)

# Communication

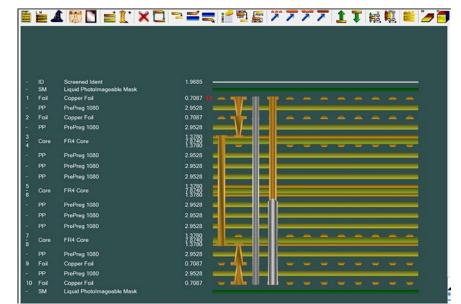

Once your stackup design is completed, then ensure it is documented and make it clear to

Figure 5: Stackup with microvia/back-drilled vias and buried vias. (Source: Polar Speedstack)

your fabricator, broker, or shop floor that you are a PCB apps engineer so that drills/backdrills, layer separation, and any transmission lines are clearly identified and associated with the relevant net classes.

### Conclusion

Keeping high speed line length as short as possible, stubs short, and careful attention to via interconnects can ease your signal integrity challenges at minimum cost. Use simple tools to flag areas where more detailed modelling or more advanced materials may prove necessary and remember that in most cases engineering is about delivering to your employer and customer the most appropriate solution for the specific application at the lowest cost. Find more information about signal integrity on our website and YouTube channel. **DESIGN007**

Martyn Gaudion is managing director of Polar Instruments Ltd. To read past columns, click here. Martyn is the author of *The Printed Circuit Designer's Guide to... Secrets of High-Speed PCBs, Parts 1 and 2.*

# In a hurry? We're the fastest in the business!

- ISO 9001:2015 Certified

- AS 9100 Rev D Certified

- MIL-PRF-31032-C Qualified

- MIL-PRF-55110 Qualified

- ITAR Registered

# Prototron Circuits America's Board Source

USAN INNI 👬

1

Serving the industry for over 35 years  $\oplus$  prototron.com & (520) 745-8515

# Your Thermal Designs Are Inefficient

# Feature Article by Douglas Brooks and Dr. Johannes Adam

Your thermal designs are (probably) inefficient. The inefficiencies are unnecessarily taking up board area and blocking routing channels. This is likely true in at least three areas:

- 1. Your high-current-carrying traces are probably too wide.

- 2. You probably use too many vias in your high-current-carrying traces.

- 3. Any thermal vias you use are (almost) worthless.

### **Trace Width**

Most designers rely on the trace widths suggested in IPC-2152<sup>1</sup>, the "bible" for calculating high-current trace widths (unless you have read our book<sup>2</sup>). IPC-2152 is the best, most thoroughly researched study of trace currents and temperatures available. But it does have some weaknesses. One weakness is that it (by necessity) studies 6-inch-long traces in isolation. But traces are not all 6-inches long nor in isolation. There are nearby design and material parameters that impact trace temperatures, most of them in a downward direction<sup>3</sup>. Perhaps the most important parameter lowering trace temperature is the presence of a plane underlying the trace. Most boards nowadays have such a plane.

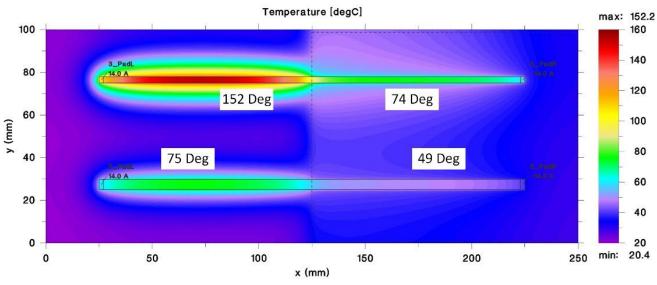

Figure 1 shows the impact a plane can have on trace temperature. It is a simulation<sup>4</sup> of two 1-ounce traces carrying 14 amps each; the top one is 120 mils wide, the bottom one is 200 mils wide. The board is normal FR-4 mate-

Figure 1: Planar impact on trace temperatures.

# A New Day Is Dawning

rial, 10" x 4", with a full plane on the bottom layer of the right-hand half of the board. The 200-mil 1-ounce trace carrying 14 amps rises to about 75°C, consistent with what we would find in the IPC tables. The temperature lowers to about 49°C over the plane. But the *smaller* 120-mil-wide trace is the same temperature (at 14 amps) over the plane as the 200-mil-wide trace is without the plane. The presence of the plane drops the temperature by roughly 50% (a result that is very situation specific).

Now, if your trace temperature specification is 75°C and you use the usual (IPC) method for determining trace size, you would design with a trace width of about 200 mils. But if you know there is a plane under the trace (or even just part of the trace), you can reduce the trace width (in this case by about 40%), opening up some additional board area for additional routing.

### Vias

Even a large trace carrying a high current often only needs a single small via to connect to another trace segment. The specific example we simulated and experimented with was the comparison of a 27-mil trace carrying 4.75 amps and a 200-mil-wide trace carrying 8.55 amps, each using a single 10-mil diameter, one-ounce plated via<sup>5</sup>. The 27-mil-wide trace via rose to a temperature of 70° while the 200-mil-wide trace via only rose to a temperature of 48°C, even though it was carrying almost twice the current<sup>5</sup>.

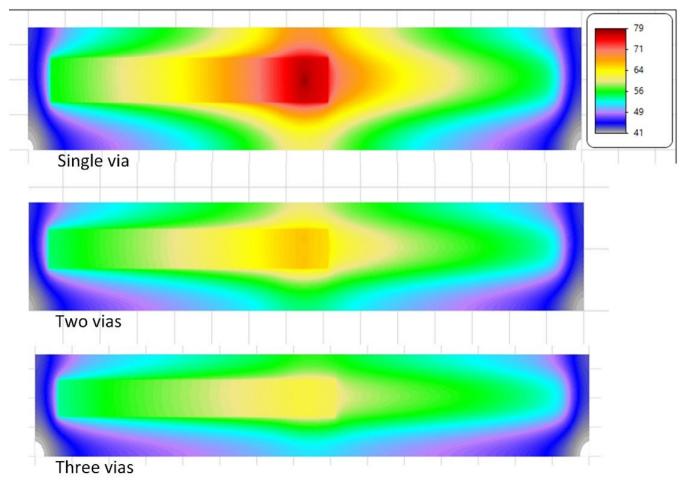

Figure 2 shows the result of another simulation<sup>6</sup>. This is of a 120 mm x 16 mm (4.7" x 0.65"), 1.55-mm (60-mil) thick board with a pair of 5-mm (200-mil) wide traces carrying 14 amps. The traces are connected with 10-mil 1-ounce plated vias. Conventional wisdom is that we should use as many vias as necessary

Figure 2: Adding vias lowers temperature to a point.

Figure 3: Heated pads, top and bottom layers.

for the total conducting cross-sectional area of the vias to equal the trace's conducting crosssectional area. In this example, that would mean 14 vias.

The top image shows the results for a single via, the middle image for a pair of vias, and the bottom image for three vias. The trace itself (without any vias) heats to about 56°C. The single via results in a via temperature of approximately 80°C, 24°C above the board temperature. This might be tolerable in some consumer applications. The use of two vias lowers each via temperature to about 67°C, 11°C above the board. Three vias results in individual via temperatures of about 62°C, only ~6°C warmer than the trace temperature itself. Adding 11 more vias only gains us about 6°C in temperature closure but locks up quite a few more routing channels.

Bottom line: We don't need nearly as many vias as our common (mis)understanding would have us believe.

### **Rules of Thumb**

Unfortunately, these illustrations are all case-specific. That is, there are no general rules of thumb that reliably flow from them. The only way to determine with any precision what gains can be made, and where, is with thermal simulations using good thermal simulators.

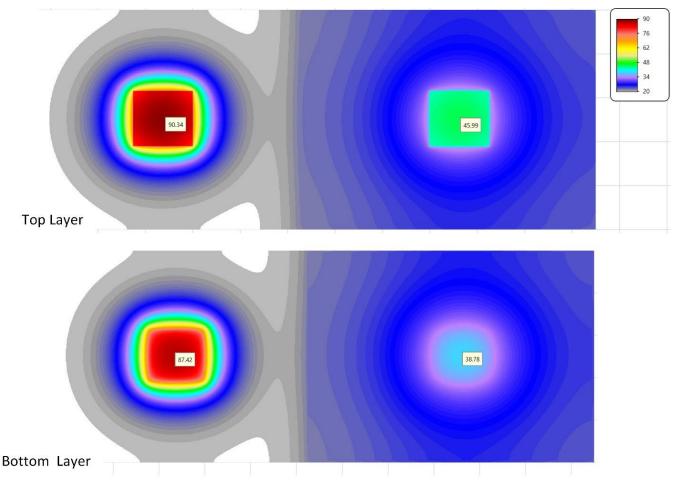

### **Thermal Vias**

Figure 3 shows a simulation using the same board as in Figure 1, but with two one-inch square heated pads instead of traces. The pad on the right is over a plane on the bottom layer. Each pad is heated by a two-watt source. The top-layer pad on the left heats to about 90°C, while the plane on the right lowers the temperature of the top-layer right-hand pad to about 46°C.

Now suppose we have the opposite situation and want to lower the pad temperature. One might think this was an application where thermal vias might be used. But thermal vias have to go somewhere, typically a plane (or at least another pad) on a lower layer, and here there is no such resource. So, thermal vias are not an option. But since there is a plane under the right-hand pad, thermal vias are an option there.

But here is the problem. Figure 3 also shows the thermal pattern on the bottom layer. What most of us fail to realize is that the thermal profile of a bottom layer of a board looks a lot like the thermal profile on the top layer. That is because the boards are typically very thin (compared to other dimensions). In this simulation the bottom board area under the top left pad is only about 3°C cooler than the pad on the top layer. The board area under the righthand pad, even though this layer is a solid copper plane, is only about 7°C cooler than the pad on the top layer. This is typical of most boards.

So, any thermal vias we drop from the top pad to the bottom plane will be mostly ineffective because the temperature difference between them is already so small. The addition of the plane has already lowered the pad temperature as much as practical.

Figure 4: Thermal profile of top pad with two thermal vias.

But that's not all. Figure 4 shows a simulation where we have placed two thermal vias under the right-hand pad. The thermal vias are 20 mils in diameter and plated to almost 3 ounces. The thermal vias are relatively large so that we can see the results in the figure. Even so, we have to zoom in optically and narrow the temperature range in order to visualize those results.

As seen in Figure 4, the pad is hotter in the center than it is around the edges. This is because the edges of a pad or trace cool more efficiently than does the midpoint. Heat can conduct away from the midpoint primarily only in the vertical (Z-axis) direction. But heat around the edges can conduct away both vertically and horizontally. All normal pads, and all traces are cooler at the edges than they are at their midpoint.

But more importantly, the thermal vias only have a small impact, and they have that only at a point<sup>7</sup>.

- 1. Each thermal via only changes the temperature by less than two degrees.

- 2. And they do so at only a very small area around the via.

That is why almost every article that discusses thermal vias recommends using a lot of them. But even if you covered the entire pad with thermal vias, the temperature still would not change by much; the gain has already been achieved with the underlying plane. The only thing thermal vias do is use up a lot of routing channels.

### Summary

By learning more about how PCB design decisions impact thermal temperatures around the board, we discover there are several areas where we can make significant impacts in design efficiencies. **DESIGN007**

### References

1. IPC-2152, Standard for Determining Current Carrying Capacity in Printed Circuit Board Design, IPC, August 2009, page 26. 2. *PCB Design Guide to Via and Trace Currents and Temperatures,* by Douglas Brooks and Johannes Adam, Artech House, 2021.

3. We talk about temperature sensitivities in Chapter 7 of our book referenced in No. 2.

4. We used a simulation program called thermal risk management (TRM), which was originally conceived and designed to analyze temperatures across a circuit board, taking into consideration the complete trace layout with optional Joule heating, as well as various components and their own contributions to heat generation.

5. See Section 8.4 of our book referenced in No. 2.

6. The maximum "pixel" resolution and density in a simulation is determined by the smallest dimension in the X-Y plane. Via simulations require about one to two orders of magnitude greater resolution than "standard" trace simulations, placing a significantly greater load on the computer CPU and memory. For this reason, modeled board areas for via simulations are typically quite a bit smaller than would be the case for regular trace simulations. This results in a slight upwards bias in model temperatures from what might be otherwise expected. *Relative* temperatures within the model, however, exhibit much smaller upward biases.

7. Temperature is a "point" concept. That is, it varies from point-to-point around a board or trace. So, too, are resistance, resistivity, thickness, and sometimes even thermal conductivity coefficients. We discuss this in numerous places in our book, and especially in Chapter 13, "Do Traces Heat Uniformly?"

**Douglas Brooks, PhD,** is a veteran signal integrity instructor and the founder of UltraCAD Design in Issaquah, Washington.

**Dr. Johannes Adam** is a thermodynamics physicist and founder of ADAM Research.

# MilAero007 Highlights

## CACI Successfully Completes Optical Communications Terminal Interoperability Testing for Space Development Agency's Transport Layer ►

CACI International Inc announced that it successfully completed Optical Communication Terminal (OCT) Interoperability Testing (OIT) of its CrossBeam<sup>®</sup> OCT for the Space Development Agency's (SDA) Tranche 1 data relay and tracking network. As part of this testing, CACI was the first SDA-compliant terminal to successfully establish a consistent data communication link with the reference modem.

# Amitron Becomes MIL-SPEC Certified >

Amitron, a leading U.S.-based manufacturer of printed circuit boards (PCB), brings an additional 80,000 square feet of manufacturing space into the overall MIL-SPEC ecosystem with high automation, and the latest equipment technology and processes for military and aerospace applications.

# Historic Wind Tunnel Facility Testing NASA's Mars Ascent Vehicle Rocket

The MAV (Mars Ascent Vehicle) team recently completed wind tunnel testing at NASA's Marshall Space Flight Center in a facility that has been a critical part of NASA missions going all the way back to the Apollo program.

### U.S. Army Awards Comtech \$48.6M for Next Generation EDIM SATCOM Solutions >

Comtech announced the company was recently awarded a \$48.6 million contract to deliver Enterprise Digital Intermediate Frequency Multi-Carrier (EDIM) modems in support of U.S. Army satellite communications (SATCOM) digitization and modernization programs.

## Lockheed Martin Conducts First Flight In U-2 Avionics Tech Refresh ►

Lockheed Martin Skunk Works, in partnership with the U.S. Air Force, completed the first flight of the U-2 Dragon Lady's Avionics Tech Refresh (ATR) program. During this mission the aircraft successfully performed a low-altitude functional check flight to integrate new avionics, cabling and software.

## Airbus Unveils PioneerLab as its New Twin-engine Flying Laboratory >

During the German National Aviation Conference in Hamburg, Airbus Helicopters unveiled the PioneerLab, its new twin-engine technology demonstrator based on the H145 platform. It complements Airbus' range of FlightLabs and focuses on testing technologies that reduce helicopter emissions, increase autonomy, and integrate bio-based materials.

# Northrop Grumman to Develop New Guided Ammunition for U.S. Navy

The U.S. Navy has awarded Northrop Grumman Corporation a development contract for the company's newly designed 57mm guided high explosive ammunition. Designated for use with the Mk110 Naval Gun Mount, the company will test and mature the munition for qualification. The 57mm guided high explosive ammunition has the unique ability to continuously maneuver in-flight as it moves toward a designated target.

# A Total PCB Solution from a Single Manufacturing Partner Rigid. Flex. Rigid-Flex. HDI. RF. Assembly.

Summit Interconnect is the largest, privately held PCB manufacturer in North America offering a broad range of highly reliable, advanced technology PCBs. With eight high-tech facilities and thousands of employees, we work alongside customers to push the boundaries of what is possible, helping to create inventive and transformative electronic products.

Summit Interconnect proudly serves these high-growth markets:

The trusted technology partner for manufacturing mission-critical PCBs.

Feature Article by Chris Young YOUNG ENGINEERING SERVICES

There are many ways, dozens to be sure, and most likely many more, to streamline a PCB design. My goal here is to pick a single-digit number of rules to abide by, that can be reasonably adhered to, and provide some bang for the buck. These rules are meant to reduce design scope creep, avoid PCB respins, and improve production yields.

# One Communicate clearly

Use explicit communication when addressing ambiguous items. Test point placement can seem like an ambiguous task. Statements like, "Find room for test points," do not help to define scope or draw boundaries. Instead, try statements like, "Production test points can only be on a single side of the PCB in order to reduce test fixture complexity." Implicit communication should be reserved for welldefined objectives and processes. An example would be instructing a PCB designer to place test points per the design procedures identified by company policy X, paragraph Y.

### Proceed with a common goal in mind

Designing on the fly without a mutually agreed upon set of goals is a catalyst for scope creep and technical debt. A design blitz, as in football, is a defensive high-risk maneuver intended to reduce schedule (offensive) pres-

# cādence°

# OrCAD X

# Design Fast. Design Correct. Design Connected.

OrCAD X brings a new era in PCB design technology where performance meets usability in a cloud-connected platform enabling data management and collaboration. Learn more about the next generation of PCB design at www.cadence.com/go/orcadx.

De\_ 1335

© 2023 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at www.cadence.com/go/trademarks are trademarks or registered trademarks of Cadence Design Systems, Inc. All other trademarks are the property of their respective owners. 11/23 DB/KK/AD-ORCDX/PDF

sure. Instead, take the time needed to establish a well-defined and measurable set of design goals. Include the project stakeholders, get buy in, and then execute.

# Three

# Design your PCB power delivery system (PDS)

Your PCB power delivery system (power planes/structures) should be based on your power distribution requirements and not a coincidence of layout. This means that your PDS design should take place before settling on a board stackup. A typical PDS is composed of discrete capacitors, power plane capacitance, and on-chip capacitance. Determining the amount of plane capacitance needed for a specific design should involve the use of a simulator such as HyperLynx, ADS, or HFSS. Designing an appropriate PDS for your board design is easy to say, much harder to do, and very much worth your time. Improper or poorly implemented PDS designs are nearly impossible to recover from without a costly board respin.

# Four Know your drill holes

A PCB can play host to many types of drill holes for various reasons. A few examples are vias, mounting holes, tooling holes, and press fit holes. Vias come in many forms, but they tend to be some type of plated hole that is typically used for signal, ground, or power transitions from one PCB layer to another. Vias can also be used for thermal conduction between PCB layers. It is important to understand that mechanical engineers typically regard mounting and tooling holes as two very different types of holes that serve entirely different purposes. Mounting holes can be plated or non-plated and provide a clearance/loose fit for the PCB so that it may be attached to some other structure. Tooling holes are designed and manufactured to a tight tolerance so they can provide a transition fit needed for precise alignment of a PCB in an assembly or test fixture. PCBs use interference fit holes for press fit connectors. The connector/PCB mating pins interfere slightly with the holes on the PCB, requiring force to be applied to the connector during the mating process instead of soldering the pins to the PCB itself. Knowing the types of drill holes used on your PCB and their purposes allows designers to effectively communicate their purposes to other stakeholders in a project.

# Five Coordinate your design with your fabricator

The last thing you want to hear from a PCB fabricator is that they are no-bidding your design because it is not compatible with their capabilities. It is perfectly reasonable to include your PCB fabricator in your design reviews. Making sure that your design fits within the manufacturing capabilities of your fabricator is a primary objective, not an "on the side" project. Furthermore, your PCBs built for production should be well within fabricator's range of capabilities and should not be pushing their edges so that your yields (major PCB cost driver) are not driven by process variations.

# Six

# Consult with the group or company assembling your boards

It is best to know what practical limitations your assembly process imposes on your design instead of finding out post assembly. Not all pick-and-place machines are created equal. Accuracy of small component placement can vary greatly between different pick-and-place machines. Manually removing assembled boards from panels can damage shock-sensitive components. The risks associated with

One Company | One Team

# Why Choose APCT?

# For Our Printed Circuit Board Technology Expertise

**Rigid Through-Hole** ~Up to 40+ Layers

HDI; Blind/Buried/Stacked Vias

- Flex Applications ~ Up to 6 Layers

- Oversized Boards ~ Up to 37" by 120"

- Rigid Flex Applications • ~ Book Binder Capability

- Heavy Copper • ~ Up to 20 oz.

# For Our Printed Circuit Board Quick-Turn Capability

Corporate Cycle Times ~ Consistently faster than industry standards

~ Up to 8x Sequential Lamination Cycles

- **Premium Cycle Times**

- ~ Quick-Turn capabilities are "World-Class"

# Why? Because Our People Make The Difference

MEDICAL INDUSTRY

**DEFENSE & AEROSPACE**

COMPUTING, NETWORKING & STORAGE

& MOBILITY

AUTOMOTIVE INDUSTRY

Capability | Capacity | Expertise Give Us The Opportunity To Earn Your Trust And Gain Your Loyalty

> APCT Leading the Printed Circuit Board Industry APCT.com | 4PCB.com

whoever may be assembling your boards can be mitigated by simply involving them in your design review process.

# Seven Document your component library process

A well-documented CAD library process reduces the chances of errors when creating parts. Part requests should include the part number, manufacturer, part description, datasheet(s), priority level, need date, package type, part type, and any descriptive information or notes for symbol or footprint creation. The part that is created to fulfill the request should be documented and linked to the request. The part should then be reviewed and documented as either meeting the request or as needing to be reworked. The documentation could take the form of a spreadsheet, database, or even a physical paper trail. The intent is to explicitly communicate what parts need to be created and how.

> *Eight* Test point placement is critical

PCB test points serve to support design and production. Circuit designers will use test

points to assist in integration and verify functionality. Test points are typically used in production to load software/firmware and verify proper PCB assembly. Production using test points should take precedence over design and engineering test points. Test point locations directly impact the complexity of test fixture design, so strive to place them on only one side of the PCB. Do not place components on the opposite side of a PCB underneath a test point. This provides space on the PCB to apply an opposing force to reduce stress and strain on the board assembly when test points are engaged during test. Don't find space for test points. Make space by performing test point placement alongside component placement. DESIGN007

### Resources

1. "Power Delivery System Design," by Lee Ritchey, Altium.

2. Simulators – Keysight ADS, Siemens EDA HyperLynx, Ansys HFSS.

**Chris Young** is founder and president of Young Engineering Services.

# **Anatomy of IPC Checklist**

# Avoid the 'Ferrari Problem' and Simplify Your PCB Design

Feature Article by Zach Peterson NWES

When I last spoke with DirectPCB cofounder Greg Papandrew, he mentioned that many boards are designed like Ferraris when what the product really needs is a Ford Pinto. Those of us who work in PCB design education, whether on corporate training or on the conference scene, tend to teach new designers how to build Ferraris. What we sometimes don't do so well is teach new designers how to identify whether a Pinto will get you safely to your destination.

So, if you need to take your Ferrari and convert it to a simpler version, how can you do it without losing your form and function? Better yet, how can you avoid the Ferrari problem altogether?

The operative word "simpler" could mean many things, and a designer's job in this area is to identify the "things" that create the most value in a design. This could be electrical performance, mechanical reliability, requirements to support a specific component type (e.g., fine-pitch BGA), or something else entirely.

### **1. IDENTIFY THE COST DRIVERS**

Any PCB that could be reasonably termed "more advanced" is more complex and thus tends to cost more. There are several factors

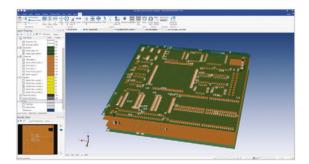

### Support For Flex, Rigid Flex and Embedded Component Designs Now Available.

- Import and Visualize Flex, Rigid-Flex and Embedded Component Designs

- 3D Visualization to Validate PCB Construction and Component Assembly

- Manage Variable Stackup Zones for Rigid-Flex Designs

- Easily Create Custom Flex or Rigid-Flex Fabrication and Assembly Documentation

#### For more information visit downstreamtech.com or call (508) 970-0670

that can drive this, which are listed in approximate order of importance:

- Type of laminate material (PTFE, advanced FR-4, etc.)

- Etch and drill feature size and processing

- Layer thickness and layer count, especially HDI build-up layer count

- High BGA/QFN count

- Expensive surface finishes

- Specialized requirements like heavy copper

Here, the key is to identify the absolute necessities that are required for your device to function to its basic specifications. There are design choices I make out of force of habit, and I have to go back and check myself based on realistic operating requirements. Keep in mind a few simple questions here:

- Do you really need a PTFE laminate in your design, or did you use it because you read somewhere that all RF boards need PTFE?

- Do you really need blind and buried vias everywhere, or can your placement and routing handle larger mechanically drilled vias?

- Is there an SI or density reason I need sub-5 mil trace widths with controlled impedance?

- Does every stub need back-drilling?

Not everyone needs heavy copper PTFE with blind/buried stacked vias and 3-mil line/ spacing. Focus on what's important and save yourself and your wallet a lot of headache. Simple steps like changes to your stackup, process limits, and material selection can create big cost savings, both in prototyping and volume production.

## 2. A LITTLE BOARD COMPLEXITY IS OKAY

This might seem like it contradicts No. 1, but I don't think this is the case. Complexity is about give and take: You add in a bit of complexity in one area, but it makes your life much easier in another area. Think blind and buried vias on a fine-pitch component: your design might work fine with neck-down routing and mechanical drilling at 6 mils, even if the conventional wisdom demands fine-line routing with stacked microvias just because your design looks like it might be HDI.

As an instructor, I've noticed that some new designers tend to think that anything over two layers is a bad design, or that the sudden addition of two internal ground planes will drop a nuclear bomb on board fabrication budgets. They end up spending a ton of time on perfect placement to minimize ghost wire crossings, and then much more time trying to route things with minimal coupling or overlap.

The reality is that four-layer boards are not advanced anymore. A board with two interior stitched ground planes is really an entry-level board, and I certainly would not call these stackups "complex." They also make routing on the top and bottom surfaces much easier, as you no longer have to worry about interlayer coupling. Then there are the EMI and SI benefits; many of the most basic SI and EMI problems can be suppressed or prevented just by using the right stackup. So, if you're new to design, give yourself permission to add a couple ground planes; your EMC testing results will thank you later.

## **3. OVER-SPECIFYING AND OVER-CONSTRAINING**

Over-constraining a design can back designers into a corner, to the point where they over-specify every net in their design rules. The corollary to this is in routing, where some EMI-worthy design features are implemented regardless of need, and they must be handled manually.

Something I've seen that is related to No. 2 is in mixed-signal design. One of the big instances where I see designers create more work for themselves is in this realm, where the most common design mistake is to create split grounds or split planes, then try to link them back together with a ferrite, capacitor, or some other EMI-inducing craziness. Even if you applied isolation correctly, it creates new routing and placement constraints that can't always be clearly defined in some CAD systems.

Another common instance here is a stitching via near a signal via. It is true that stitching vias are needed when changing layers or references, but do you really need to painstakingly add this manually to every signal via? Find the main single-ended signals that really need it, such as your SPI bus. Noise margins on your configuration lines are very often large enough that you don't need to throw a stitching via on these. Think about the context of the rule; don't just follow it blindly.

#### Keep it Simple, Save the Headache

The trick to stepping up your design game is not about knowing advanced design techniques but knowing when to implement them. I've met some designers who are decades my senior but still fall victim to this mistake. Those of us who educate designers have to take a bit of responsibility for this. It's our job to provide context for these rules so our peers can avoid the Ferrari problem.

When you do find that you need your design techniques, learn to leverage your tools for these engineering problems. Higher-end CAD programs have the automation tools needed to create more advanced design constraints. Take time to learn these techniques and you will set yourself up for success. **DESIGN007**

Zach Peterson is the founder of Northwest Engineering Solutions as well as a PCB design instructor and podcast host.

### Brandy Tharp: A Passion for Helping Others

Eleven-year-old girls hold many interests, from sports and playing games, to learning how to make more complex decisions and finding commonalties with friends and loved ones.

While Brandy Tharp may have been doing all those things at that age, she was also learning a new skill that most of her friends probably weren't—how to solder. It lit a fire in this young girl who enjoyed math, helping others, and finding ways to harness her energy.

"My mom taught me how to solder on rechargeable battery units that she built," says Brandy, director of education at IPC. "It was something I grew up with. Everybody kind of fell into some facet of the field."

When she started college, Brandy also worked for a telecommunications equipment manufacturer doing hand insertion manual assembly, then learning how to run a wave solder machine because she could work a weekend shift.

"But I'm not the kind of person who can sit still," she says. "I like to know a little bit about everything." Because the company was short on operators, Brandy learned how to program and run more lines and equipment, working her way through each department. That led to a position in the training department and launched a career in training and certification.

Continue reading in IPC Community.

# Best Practices for Ensuring PCB Design Manufacturability

#### **Connect the Dots**

by Matt Stevenson, SUNSTONE CIRCUITS

It makes sense to optimize your board using design for manufacturability (DFM) techniques, but applying DFM best practices can be confusing without formal training. The results are designs that are often incomplete, poorly designed, or too complex.

When these issues arise, your PCB manufacturing partner rejecting the design can be considered a best-case scenario because it means they have your back. If your design is simply dropped into an automated queue without concern for manufacturability, the output can be a batch of unusable boards.

Expensive mistakes can be avoided by adopting practices that encourage design for manufacturability. In addition, carefully choosing a manufacturing partner and service level that align with your needs will help you achieve a quality result.

Let us examine some design best practices that will help reduce costs, increase yield, and improve manufacturability.

# Allegro X

## NEXT GENERATION PCB DESIGN

1 = = = = = = = =

OFFERING ENGINEERS THE INDUSTRY'S FIRST SYSTEM DESIGN PLATFORM THAT INTEGRATES LOGIC/PHYSICAL DESIGN, SYSTEM ANALYSIS, AND DESIGN DATA MANAGEMENT FOR PC3 AND SYSTEM DESIGN.

GET STARTED TODAY >>

EMA Design Automation\*

.....

\*\* 88

#### **Study the Rulebook**

It is up to you to be familiar with the design rules. Not every manufacturer prioritizes making DFM rule sets for popular design tools available, cost-effective, and current. Working with a manufacturer who does make rules available will save time and money.

Of course, using design rule checks (DRC) alone will not guarantee manufacturability, but performing them is a great way to ensure that you have created as close to an error-free design as possible.

Remember that error-free is an unattainable point on the horizon you can almost see, but never quite catch. The goal should be a design that lowers the risk of defects and can then be manufactured and assembled. The DRC will help you identify conflicts, such as issues with insufficient clearances between electrical conductors, that will affect electrical functions and create potential manufacturability issues.

#### **Always Review Your Design**

We strongly encourage you to always review your design. Take a second look for issues such as insufficient power trace widths, blind vias, and components that are laid out too close together. When a design pushes the manufacturer's tolerances, it is easy to accidentally cut holes or route slots too close to pads or traces.

Copper thickness is another important design consideration. Higher current may require thicker copper and narrow traces probably should be thinner. Be specific about what you need to ensure your design will not fail. Check land patterns against the part supplier's manufacturer datasheets (MDS) as well. Often, that is all it takes to avoid common design issues.

#### **Consider How Your End Product** Will Be Used

Your manufacturing partner does not know what type of device the board will be part of, or the conditions in which it will have to perform. It's common for harsh environments or exposure to interfere with a board's performance. To avoid catastrophic failure down the road, you must call out materials that will tolerate the final product's operating environment. Be sure your board and components can tolerate thermal stress or solder joints risk breaking and damaging components.

0

С

Discover the newest innovations and hear from the best minds in the electronics manufacturing industry. IPC APEX EXPO 2024 is our industry's largest event in North America, and this year's event will feature the largest gathering of leading

WHAT'S

NEXT

BECOMES

manufacturing industry. IPC APEX EXPO 2024 is our industry's largest event in North America, and this year's event will feature the largest gathering of leading manufacturers, suppliers, and product innovators, a technical conference with highest level of quality and technical merit through peer-reviewed technical paper presentations, professional development courses featuring knowledge you can leverage right away, non-stop networking opportunities and much, much more! Join us in Anaheim, California, April 6-11, 2024, as IPC APEX EXPO host the Electronic Circuits World Convention 16 (ECWC16).

#### Adhere to the Principles of DFM

We recommend integrating all these best practices into a design process that looks forward to the manufacturing process. Finding issues earlier makes them cheaper and easier to fix. From the outset, perform all design tasks while considering yield and other manufacturing issues that affect cost and quality.

Communicate with your manufacturing partner regularly throughout the design process. They can do more than just find problems. A good manufacturing partner has valuable insight into how design decisions impact manufacturability, yield, and quality of the boards.

Each manufacturer has unique capabilities and process requirements that can have a large impact on the manufacturability of your design, making an open line of communication critical. For example, your suppliers can confirm that you are using up-to-date footprint files throughout the design process. Highly manufacturable designs exist within a range of specifications. Manufacturers can often help you tweak your design to make the best use of these ranges. Designer/manufacturer communication about DFM can help save time, reduce costs, and even improve the functionality of your board.

#### **Help When You Need It**

Choosing a manufacturing partner with readily available support staff can help you solve manufacturability puzzles during the design process, rather than after submission. It's useful to ask a few questions of any potential manufacturing partner before deciding.

- Is competent technical support available when you need it?

- How quickly will they respond to your needs?

- Email is slow, so how can you get support for time-sensitive issues?

- What is their escalation policy for difficult support requests?

- What support packages are available and how much do they cost?

The real key to optimizing the manufacturability of your PCB designs is choosing the right tools, process, and manufacturer that meet the needs of your design. Treat your parts suppliers, PCB manufacturer, and PCB fabricator as members of your design team. Prioritize open and persistent collaboration with each of them.

Good communication and adherence to a DFM-focused process will ensure board quality, manufacturability, and cost-effectiveness. **DESIGN007**

Matt Stevenson is vice president at Sunstone Circuits, a division of American Standard Circuits. To read past columns, click here. Matt is also the author of *The Printed Circuit Designer's Guide to... Designing for Reality.*

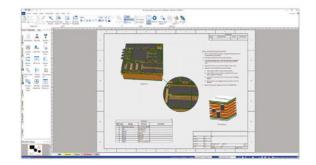

## Integrated Tools to Process PCB Designs into Physical PCBs

Use manufacturing data to generate a 3D facsimile of the finished product.

nsure that manufacturing data is accurate for PCB construciton.

Verify and Optimize PCB Designs for Successful Manufacturing BluePrint-PCB Create Comprehensive Documentation to

Create Comprehensive Documentation to Drive Fabrication, Assembly & Inspection

DownStream Technologies, offers an integrated manufacturing data preparation solution for PCB post processing including manufacturing data visualization, stack-up definition, PCB panel visualization and support for 3D PCB documentation. This environment allows PCB designers and engineers to visualize, verify and document a printed circuit board before manufacturing.

800-535-3226 downstreamtech.com ©2019 DownStream Technologies, Inc. All rights reserved.

# Take It From Scotty: Simple Really Is Better

#### **Tim's Takeaways**

Feature Column by Tim Haag, FIRST PAGE SAGE

I am, at heart, a die-hard "Star Trek" fan. When I was a kid, I was all about phasers, warp drive, and cool stuff like that. However, these days, I tend to put a higher value on production and storytelling. But like any fan (I'm avoiding "Trekkie" because, frankly, it's kind of embarrassing), certain moments from the hundreds (if not thousands) of hours filmed for the various TV shows and movies are among my favorites. One of those moments is in "Star Trek III, The Search for Spock," when our heroes steal the Starship Enterprise from space dock. The space dock scene is a pivotal moment in the movie. It is highlighted by excellent character interaction, humor, amazing music by the late great James Horner, and marvelous (for its time) special effects and cinematography. After some careful maneuvering to get the Enterprise out of space dock, Kirk and the crew fly away at warp speed, leaving their pursuers in the dust thanks to a little sabotage on the part of Scotty, the chief engineer. As it turns out, Scotty had previously removed some crucial components from the pursuing ship, causing their new and fancy computer to fail, and allowing the Enter-

Hmm, what is the recommended **minimum solder mask** width to be able to get a solder mask bridge **between two copper pads?**

PCBs are complex products which demand a significant amount of time, knowledge and effort to become reliable. As it should be, because they are used in products that we all rely on in our daily life. And we expect them to work. But how do they become reliable? And what determines reliability? Is it the copper thickness, or the IPC Class that decides? Every day we get questions like those. And we love it. We have more than 500 PCB experts on 3 continents speaking 19 languages at your service. **Regardless where you are or whenever you have a question**, contact us!

What's your PCB question? www.ncabgroup.com/pcb-design-mistakes/

#### **Reliable** answers. **Reliable** PCBs.

prise to make a clean getaway. The scene ends with Scotty's sarcastic comment about the overly complicated computer on the other ship, "The more they overthink the plumbing, the easier it is to stop up the drain."

I've always liked Scotty more than anyone else on that show because, let's face it, he was an engineer. But with this movie, I really came to appreciate his common sense and, if I'm being honest, the sarcasm he used to describe it. Even in a universe where transporter beams and deflector shields are as common as the Keurig on my kitchen counter, Scotty still knew when something was too com-

plex to be practical. Wise words, and a lesson here for everyone.

In our industry, we design and manufacture amazingly complex electronics. I've laid out circuit boards for everything from large computer systems to small

wearable devices, and even though they have had different degrees of design difficulty, they all had the same common objective: They all had to work correctly once they were built. To accomplish this, circuit boards are designed according to several standards to ensure they can be manufactured and work as intended. If you are in the design and layout part of this business, you are no doubt already familiar with many of these different standards. But once you go beyond the industry standards and into the realm of rules, processes, and procedures, the water can get murky.

Take, for instance, the rules and constraints we use in the CAD system to design the board. These are wonderful tools and an essential lifeline for both design and manufacturing, but they can work against you if you aren't careful. Let's look at a couple of ways this can happen:

• **Too many rules:** Our design databases can become afflicted with the same problem that Scotty alluded to, where overthinking

the plumbing can stop up the drain. For example, instead of defining a unique rule for each net and thereby managing thousands of rules, group your nets together according to their needs and assign them all to a single net class. This will save you time and system resources.

• Lack of understanding: It is important to be very familiar with what your PCB design CAD system will do with the rules you feed it. I've seen some databases where rules have clashed with each other,

like keep-out areas that block a cop-

per pour that is supposed to connect to a specific net in that area. If you don't rethink and redefine the rule, you have to either break it or turn checking off.

• Old data: Sometimes CAD databases get inundated with rules they simply don't need. This can happen when people read in stock rules from their corporate library, fail to clean out older rules already in their databases, or both. I've opened up some designs that have rules not even intended for that design but reside in the database, taking up additional resources.

Mismanaged design rules can overload your system as well as generate unexpected results. I'll summarize here by saying it is imperative that PCB designers know what rules are loaded into their systems and optimize those rules for the best performance of their design tools. But design rules are just part of the murky waters I described earlier. Now, let's look at processes and procedures for a moment.

Processes and procedures are an essential part of any design department. They organize the workflow, ensure that the proper steps, checks, and balances are in place, and serve as a guide to the users in the department. How-

Mismanaged design rules can overload your system as well as generate unexpected results. Hmm, what is recommended minimum distance for copper to board edge?

PCBs are complex products which demand a significant amount of time, knowledge and effort to become reliable. As it should be, because they are used in products that we all rely on in our daily life. And we expect them to work. But how do they become reliable? And what determines reliability? Is it the copper thickness, or the IPC Class that decides?

Every day we get questions like those. And we love it. We have more than 500 PCB experts on 3 continents speaking 19 languages at your service. **Regardless where you are or whenever you have a question**, contact us!

What's your PCB question? www.ncabgroup.com/pcb-design-mistakes/

#### **Reliable** answers. **Reliable** PCBs.

ever, processes and procedures are not everfresh on their own. They can get stale quickly and must be reviewed regularly to look for areas needing optimization and enhancement.

For example, do you remember many years ago when PCB designers had to create an aperture list with every set of Gerber files that was sent out? I remember how I used to manually optimize my traces and pad sizes

to match the limited amount of aperture positions on the mechanical aperture wheel in the photoplotter. Thankfully, apertures began to be included in the Gerber file when the file format was updated to RS-274X, which certainly made life much more convenient for me as a designer. And yet, many design department processes and procedures continued to insist that a separate aperture file still had to be created along with the set of Gerbers. Why?

Look at the processes and procedures you have in place to determine whether you can increase your and your staff's overall efficiency. Here are some areas to keep an eye out for:

- Design reviews: These meetings are essential, but do you need the same reviews you've always done? Many design reviews are driven by the needs and technologies of the time, so something may have changed and made some of these reviews redundant. On the other hand, some of your newer processes may reveal the need for an additional review at a spot you didn't expect.

- Workflow: Just as with the aperture list, areas of your documented workflow may have changed. Over time, you and your staff probably have adjusted to these

changes without realizing it, and you could be in for some surprises when you hire and train someone new.

• SOPs: Like the workflow documentation, CAD departments often have a bunch of SOPs to help with everything from how to create a padstack to filling out a timecard. While SOPs like this should be documented, more often than not they exist as

> hidden text files and sticky notes. Here is where open communication is essential to ensure that everyone in the department is aware of process changes and where to find official documentation on how to stay current with these changes.

> > To keep our department processes from getting "stopped up," we must work diligently to prevent our workflows from being unnecessarily complex. As we have seen, this includes not

only the processes and procedures that guide our groups in their daily work, but also the design rules and constraints used to lay out a circuit board. Until next time, keep on designing everyone—and yes, "live long and prosper." **DESIGN007**

Tim Haag writes technical, thought-leadership content for First Page Sage on his longtime career as a PCB designer and EDA technologist. To read past columns, click here.

To keep our department processes from getting "stopped up," we must work diligently to prevent our workflows from being unnecessarily complex.

FALL 2023

### **O** LOOK INSIDE

Contact us to become an advertiser

# Just a Matter of Time

#### **Beyond Design**

by Barry Olney, IN-CIRCUIT DESIGN PTY LTD / AUSTRALIA

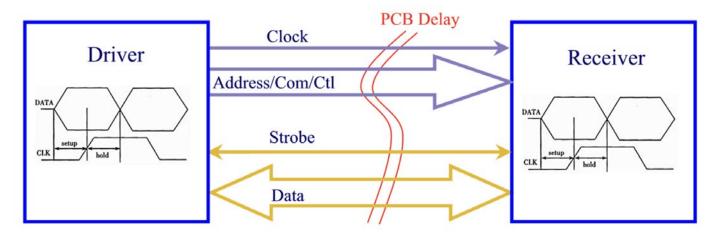

Electromagnetic energy propagates at about half the speed of light within the dielectric of a multilayer PCB. This speed is inversely proportional to the square root of the dielectric constant (Dk) of the material. The lower the Dk, the faster the propagation of the wave. In the past, we ignored the boardlevel delay as it was relatively instantaneous compared to the slow rise time of the signal waveform. But now that we have entered the realm of Gigabit/s design, an unaccounted 10 ps of delay can mean the difference between success and absolute failure of a high-speed design. Also, the trend is toward lower core voltages, which conserves power. However, reducing the core voltage also reduces the noise margin and impacts the system timing budget.

We are dedicated to excellence through INDOVATION INDOVATION SECTIONAL INDOVATION INDOVATIONI INTICO INDOVATIONI INDOVATIO

**COMMERCIAL • MILITARY • MEDICAL • BAREBOARD**

Table 1: Overall DDR3-1066 timing budget allowances and resulting margin

| Parameter                                  | Setup (ps) | Hold (ps) |  |

|--------------------------------------------|------------|-----------|--|

| Open window from simulations               | 456        | 631       |  |

| SDRAM setup and hold times from datasheets | 25         | 100       |  |

| Slew rate derating if >1V/ns               | 2.3        | 2.8       |  |

| Timing offset with respect to VREF         | 13         | 11        |  |

| SDRAM derating                             | 88         | 50        |  |

| Crosstalk                                  | 47         | 42        |  |

| Controller error – skew                    | 200        | 200       |  |

| Clock error – jitter                       | 30         | 30        |  |

| PCB routing tolerance                      | 10         | 10        |  |

| Margin                                     | 41         | 185       |  |

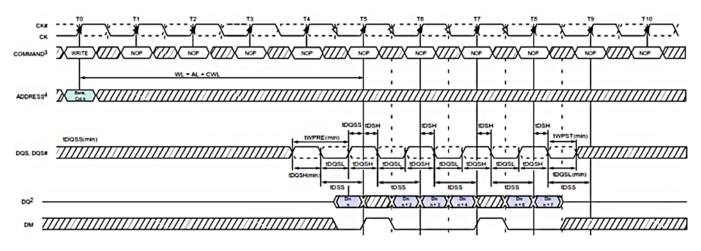

Designing a memory interface is all about timing closure. Each signal's timing needs to be compared to the related clock or strobe signal in such a way that the data can be captured on both the rising and falling edge of the strobe hence the term double data rate (DDR). The increase of data rates to 7800 MT/s for DDR5 has made the timing margin associated with each rising and falling edge even tighter.

Table 1 lists the various timing delays of a DDR3 memory interface running at 533 MHz. After allowing for the chip-level delay, setup and hold times, slew rate derating, clock skew, and jitter we are left with a total margin of just 41 ps on the setup time. Even at this relatively low clock frequency of 533 MHz, 10 ps is all the margin we have left for the board-level delay. Increase the crosstalk or jitter and we are looking at imminent system failure. So, the velocity of propagation of the electromagnetic wave of energy through the PCB is now very significant.

Most systems, whether at the chip or board level, operate synchronously; as such, voltage levels must rise or fall within a specified time or else the circuit will be out of sync and failures will occur. The timing budget tells us how much margin we have, or to put it another way, how much headroom we have before a failure occurs.

So, how do we go from a timing spec (Figure 1) to the actual flight time of the entire memory interface?